## 3048 MS

# HP 8663A SYNTHESIZED SIGNAL GENERATOR (Including Options 001, 002, & 003)

## Service Manual

#### Volume 2

#### SERIAL NUMBERS

This manual applies directly to instruments with serial numbers prefixed:

2234A to 2927A and all MAJOR changes that apply to your instrument.

rev.01JUL91

For additional important information about serial numbers, refer to "INSTRUMENTS COVERED BY THIS MANUAL" in Section 1.

#### Third Edition

This material may be reproduced by or for the U.S. Government pursuant to the Copyright License under the clause at DFARS 52.227-7013 (APR 1988).

Copyright@HEWLETT-PACKARD COMPANY 1982 EAST 24001 MISSION AVENUE, TAF C-34, SPOKANE, WASHINGTON, U.S.A. 99220

Service Manual (Volume 1, 2, 3, 4) HP Part 08663-90071

Other Documents Available: Operation and Calibration Manual HP Part 08663-90069 Microfiche Service Manual HP Part 08663-90072 Microfiche Operation and Calibration Manual HP Part 08663-90070

Printed in U.S.A. : November 1990

#### **COPYRIGHT AND DISCLAIMER NOTICE**

Copyright – Agilent Technologies, Inc. Reproduced with the permission of Agilent Technologies Inc. Agilent Technologies, Inc. makes no warranty of any kind with regard to this material including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Agilent Technologies, Inc. is not liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material or data.

Volume 2 Contents

-/

.

.

## **VOLUME 2 CONTENTS**

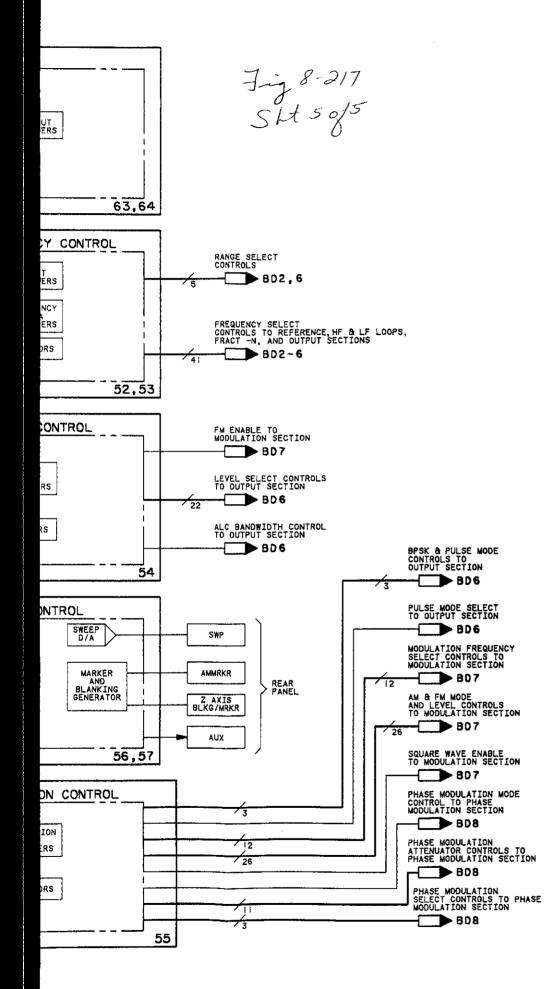

| Schematic<br>Service<br>Sheet<br>Number | Block<br>Diagram | Assembly or Section |                                                 | Theory/Trouble-<br>Shooting<br>Page<br>Number | Parts<br>List<br>Page<br>Number |

|-----------------------------------------|------------------|---------------------|-------------------------------------------------|-----------------------------------------------|---------------------------------|

| BD1                                     | _                |                     | Overall Block Diagram (Instrument Level)        | 8-201                                         | _                               |

| BD2                                     |                  |                     | Reference Section                               | 8-213                                         | _                               |

| BD3                                     | —                |                     | High Frequency Loops Section                    | 8-217                                         | _                               |

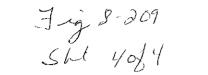

| BD4                                     | -                |                     | Fractional-N Loops Section                      | 8-223                                         | —                               |

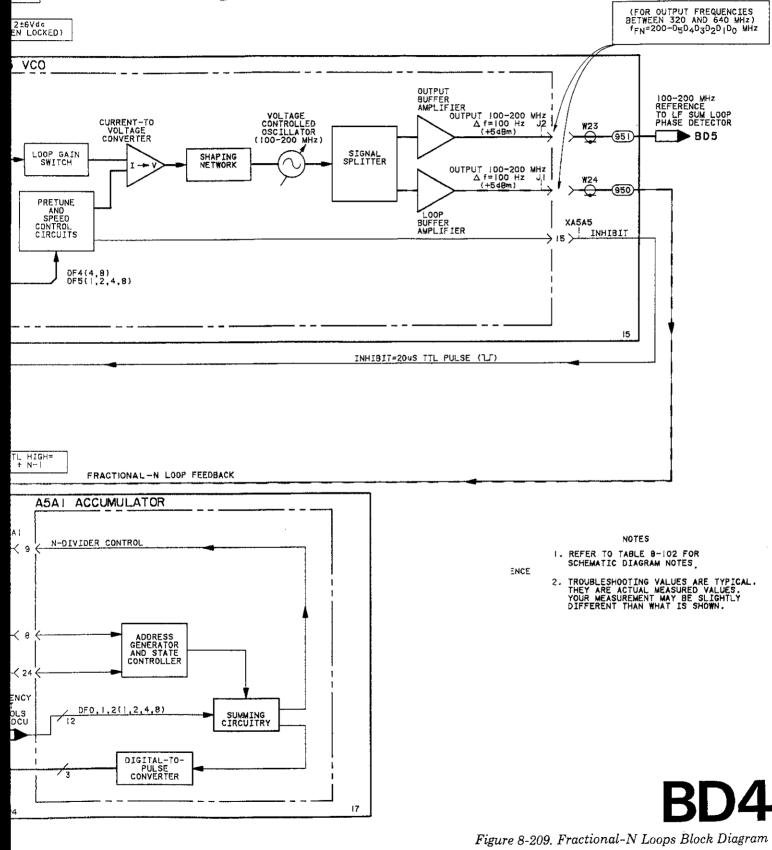

| BD5                                     | <b>—</b> .       |                     | Low Frequency Loops Section                     | 8-233                                         | _                               |

| BD6                                     | ****             |                     | Output Section                                  | 8-241                                         | _                               |

| BD7                                     | · _              |                     | Modulation Section                              | 8-249                                         | _                               |

| BD8                                     | —                |                     | Phase Modulation Section                        | 8-257                                         | _                               |

| BD9                                     |                  |                     | Digital Control Unit (DCU) Section              | 8-261                                         | _                               |

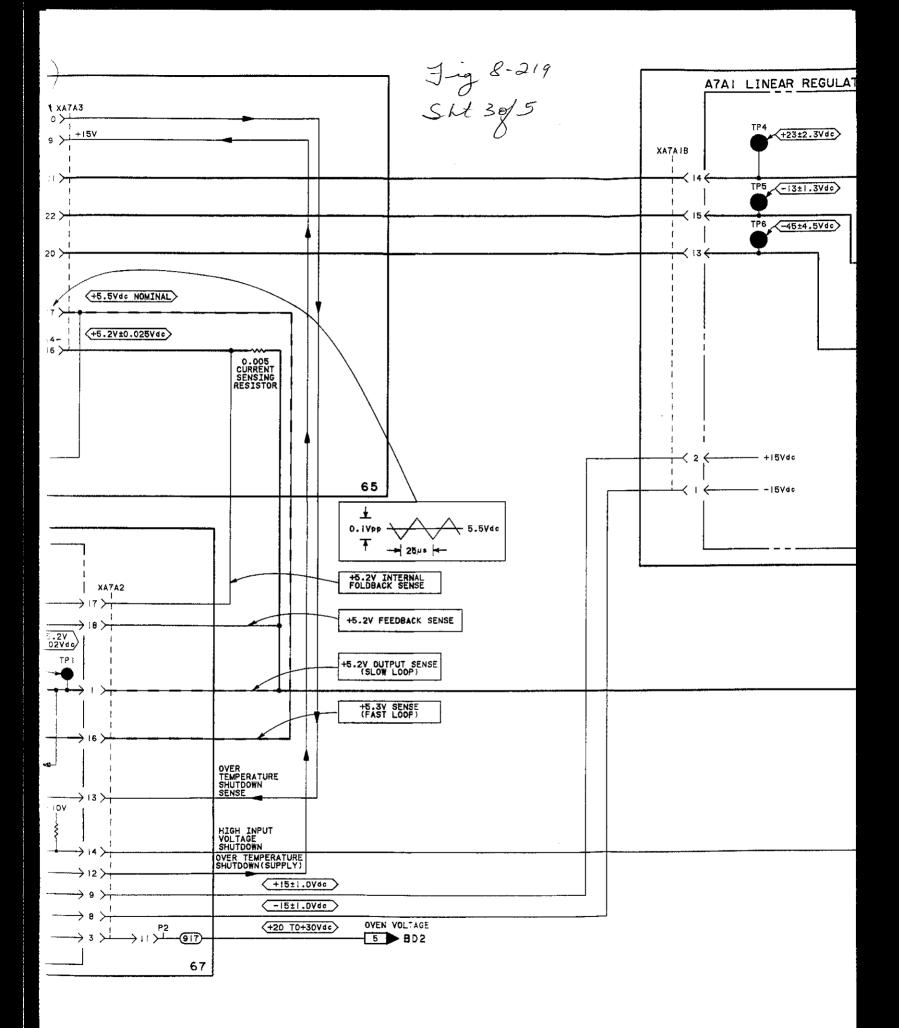

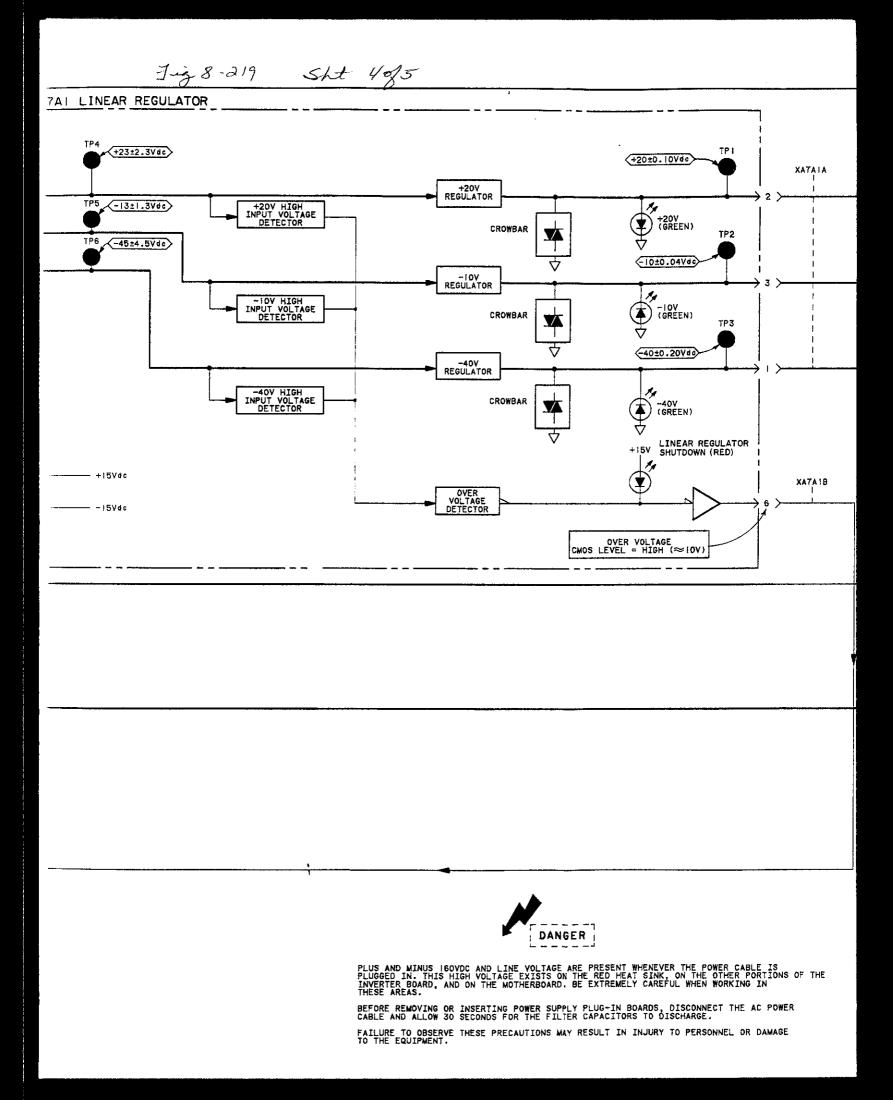

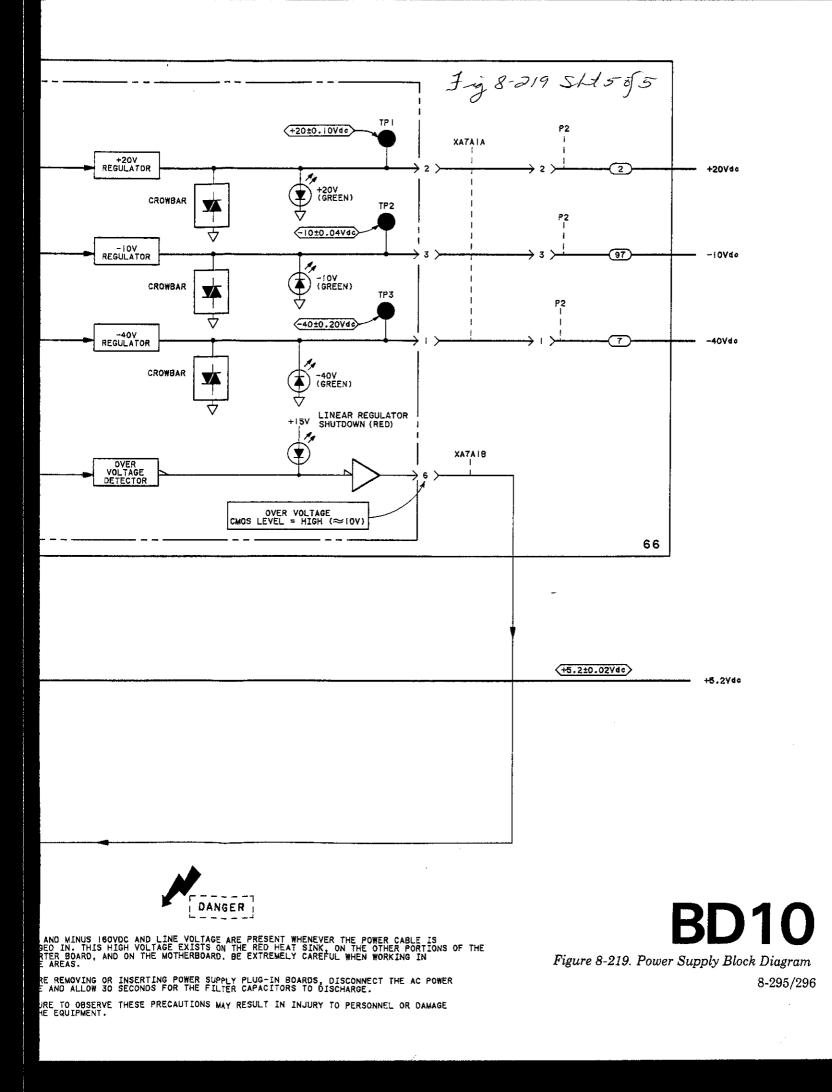

| BD10                                    |                  |                     | Power Supply Section                            | 8-289                                         | _                               |

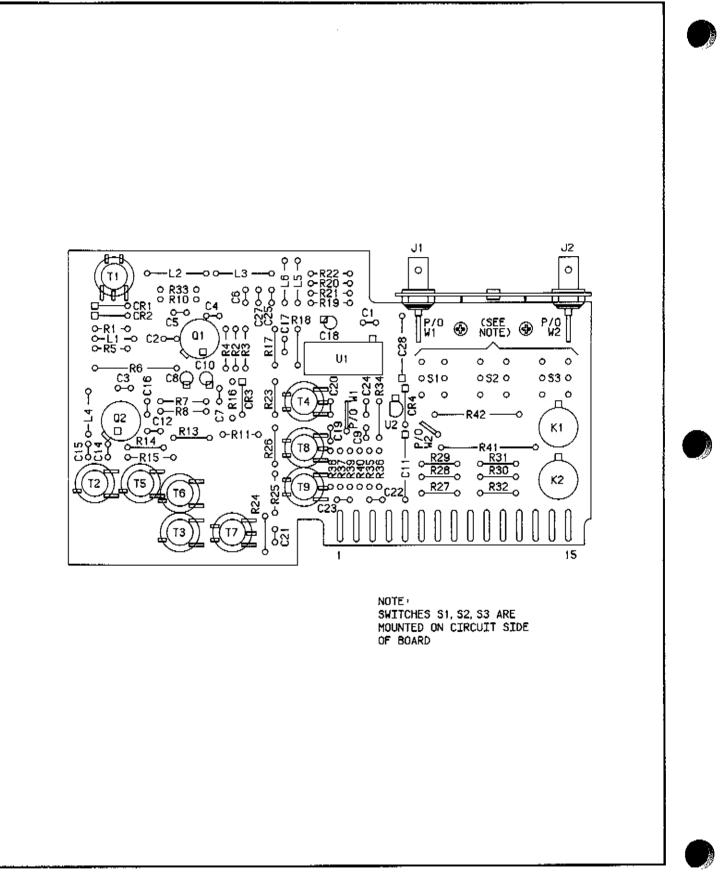

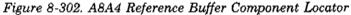

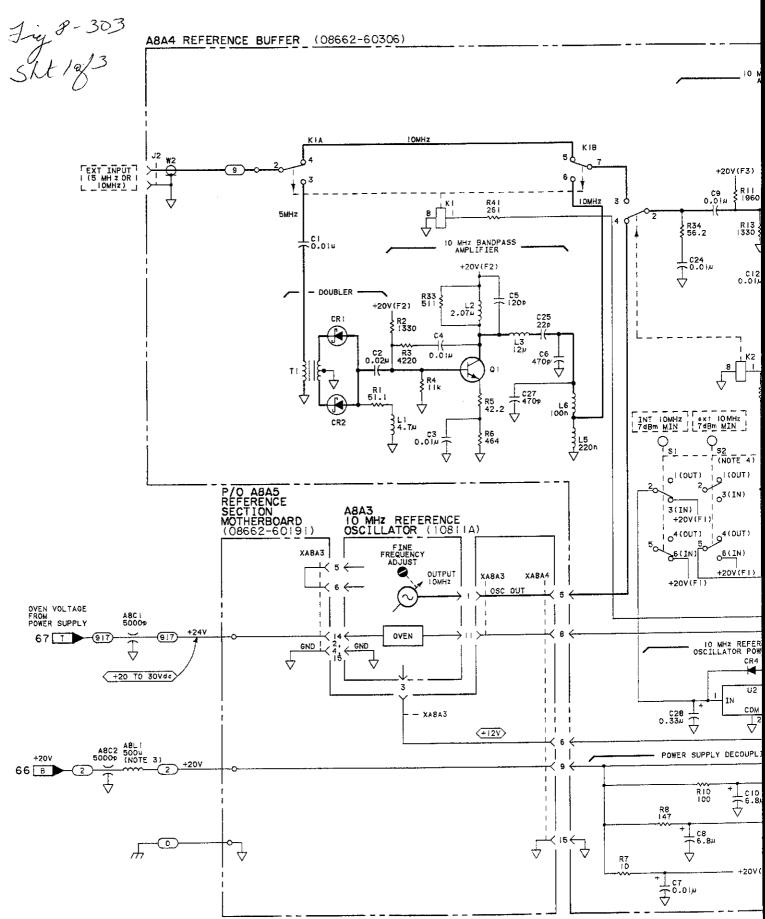

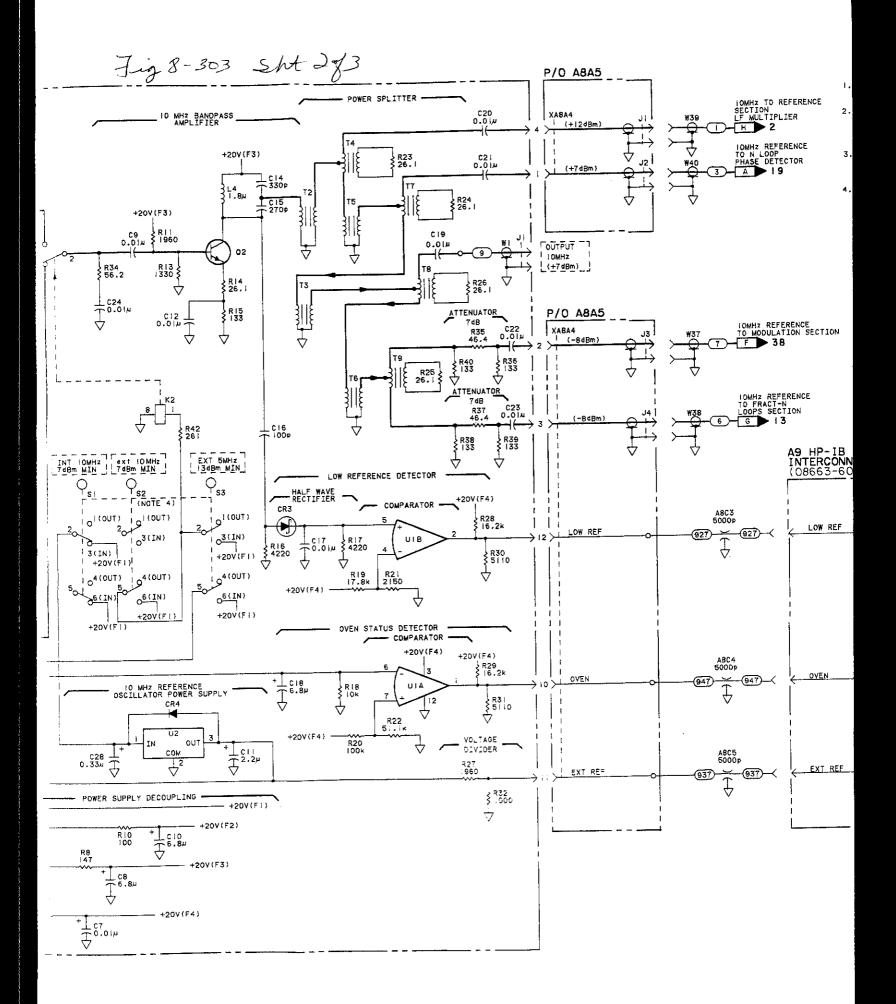

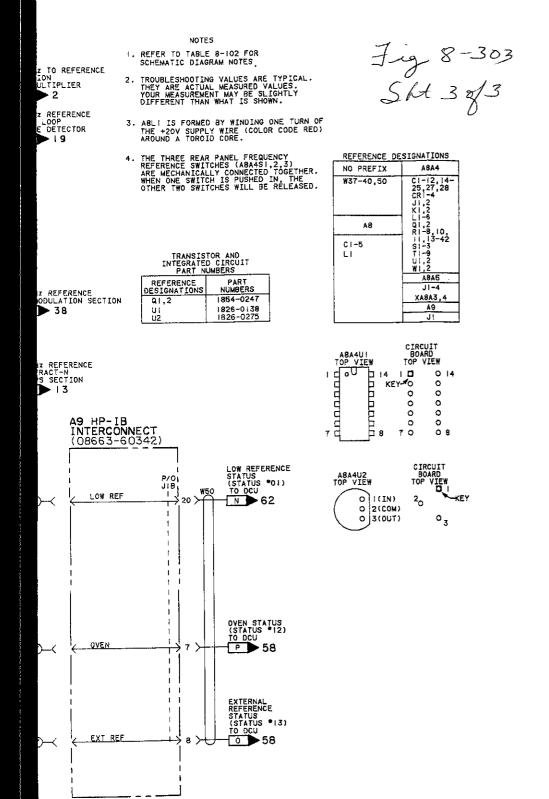

| SS1                                     | BD2<br>BD2       | A8A3<br>A8A4        | 10 MHz Reference Oscillator<br>Reference Buffer | 8301                                          | 6–176                           |

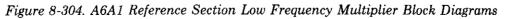

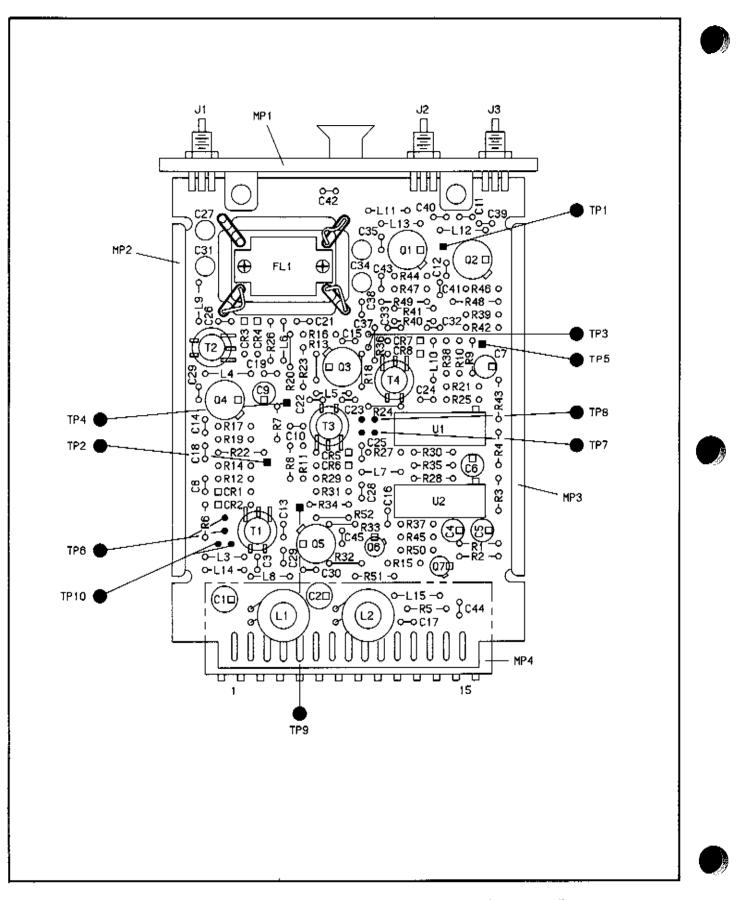

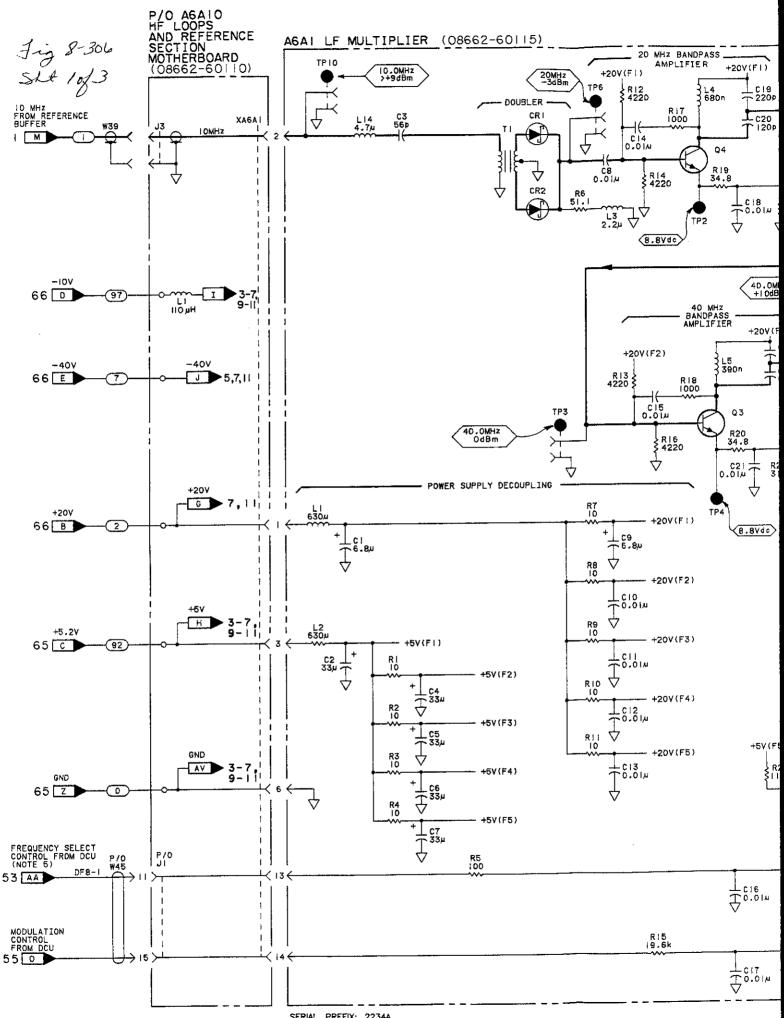

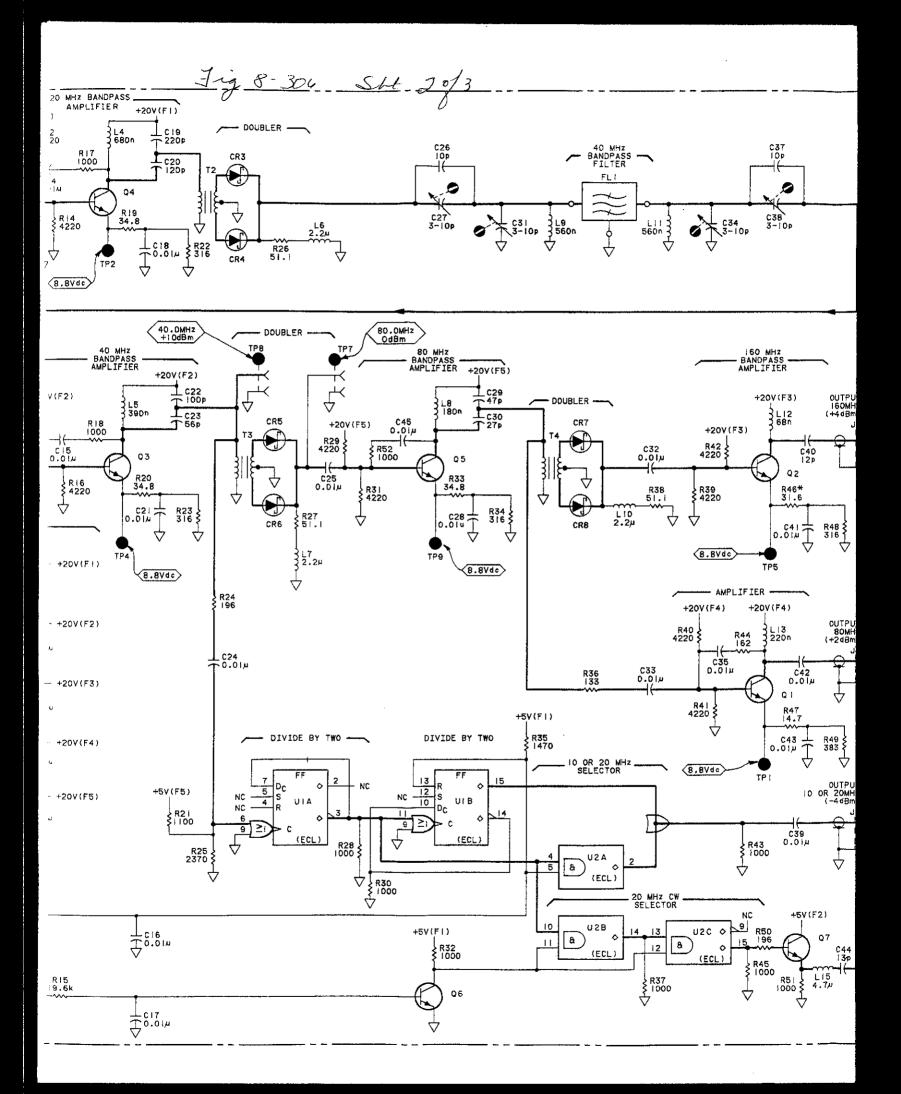

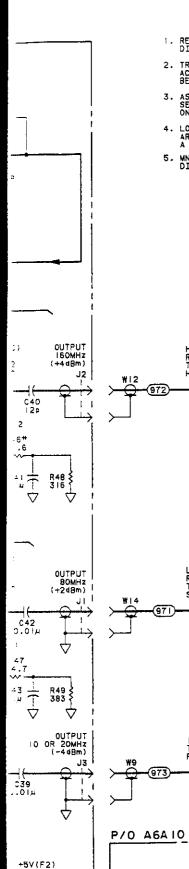

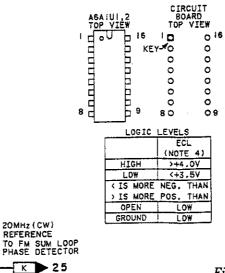

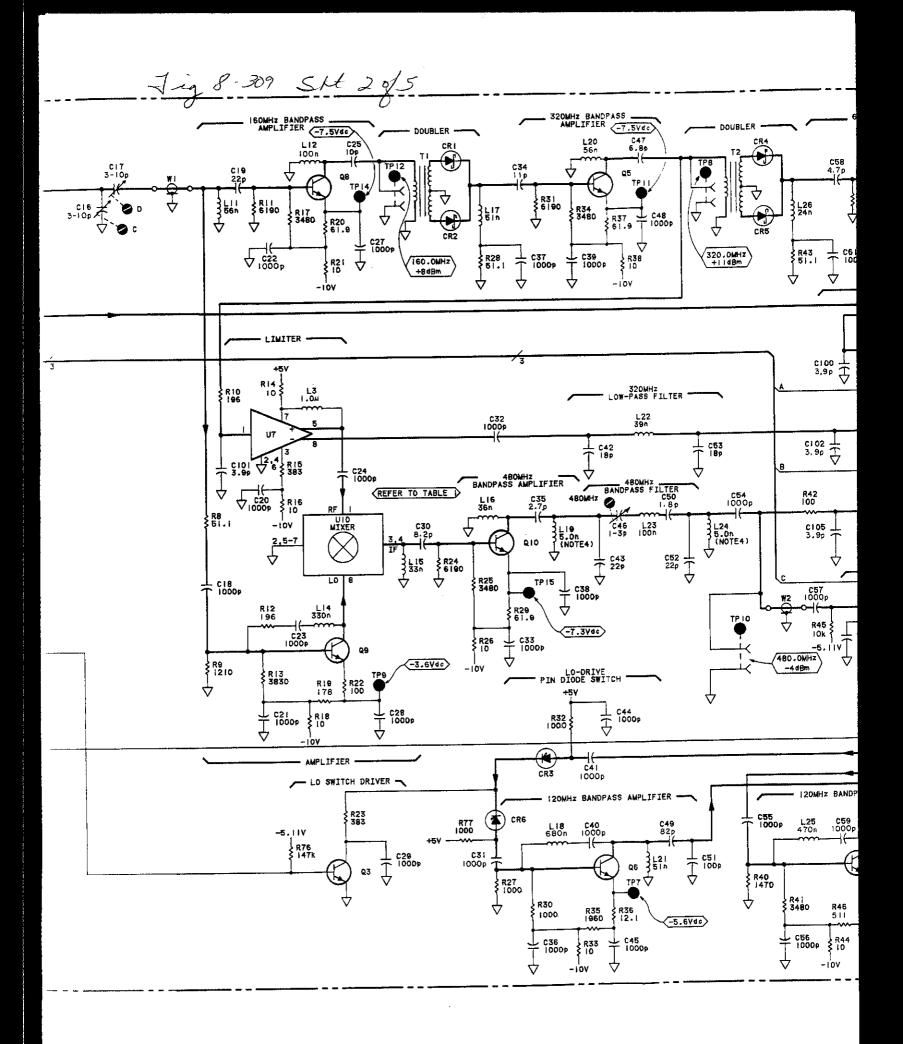

| SS2                                     | BD2              | A6A1                | Reference Section LF Multiplier                 | 8-307                                         | 6-117                           |

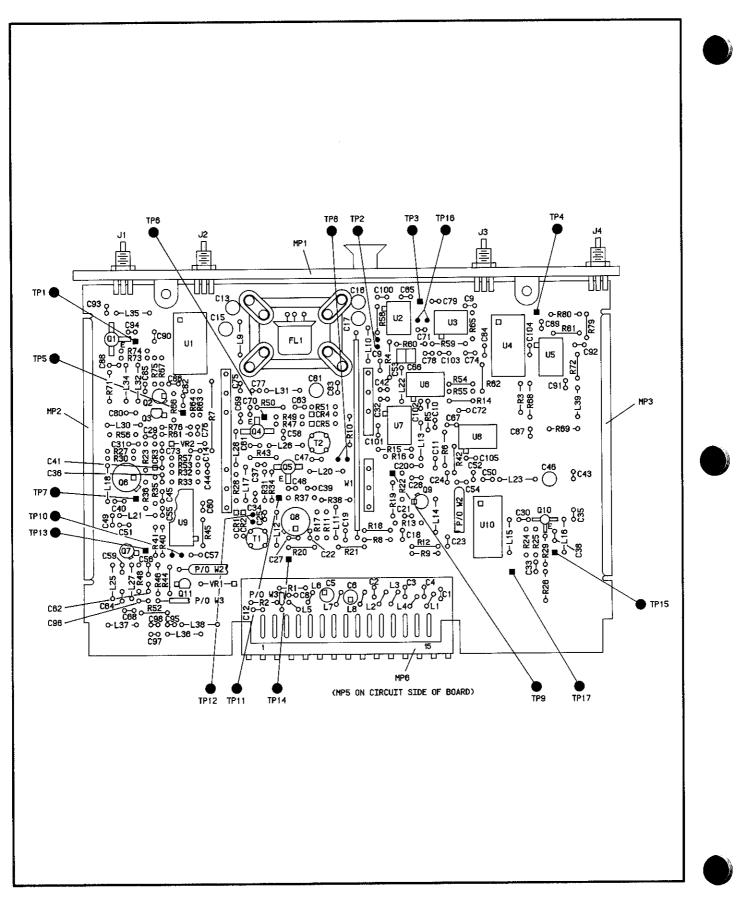

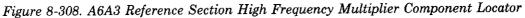

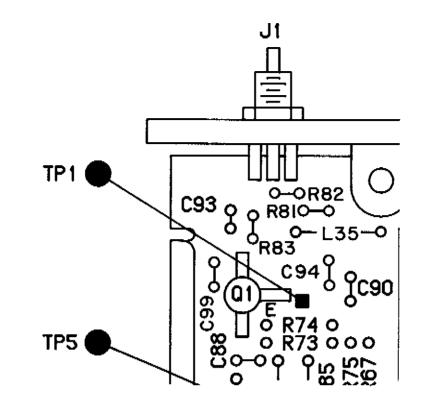

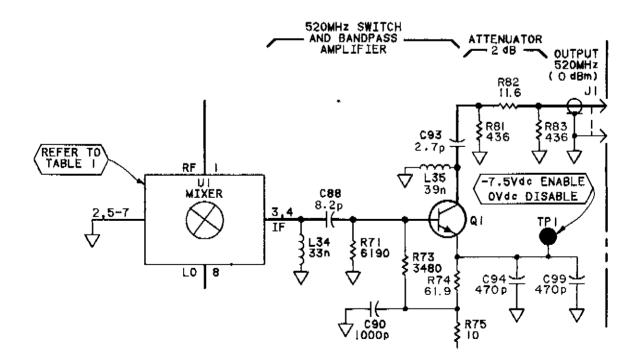

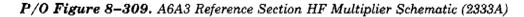

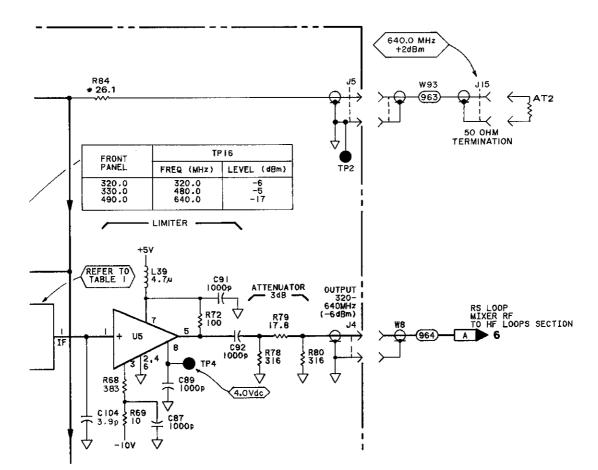

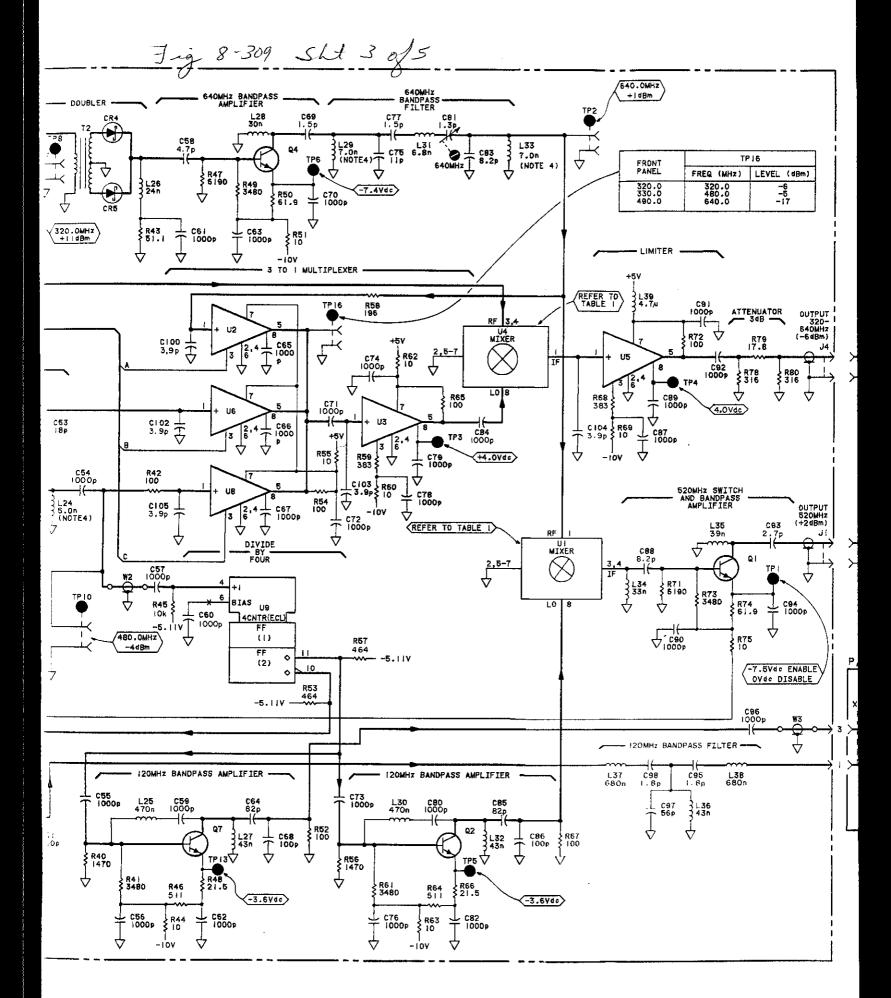

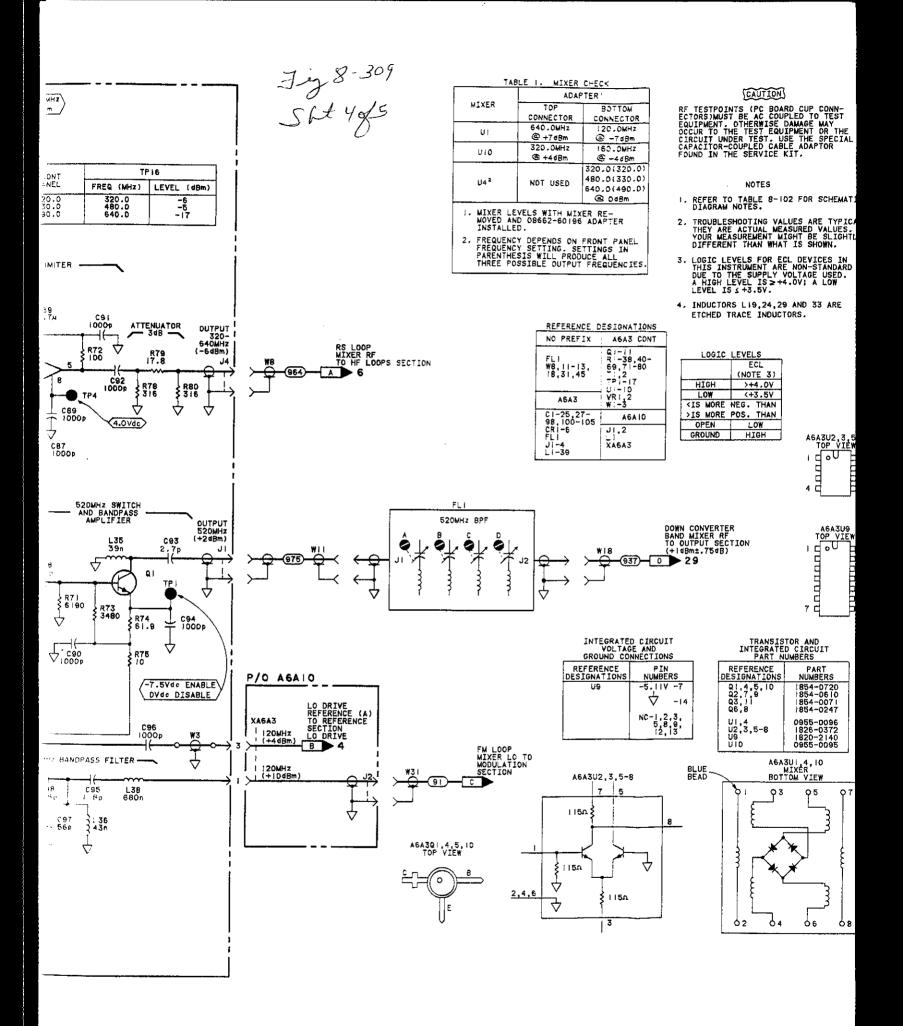

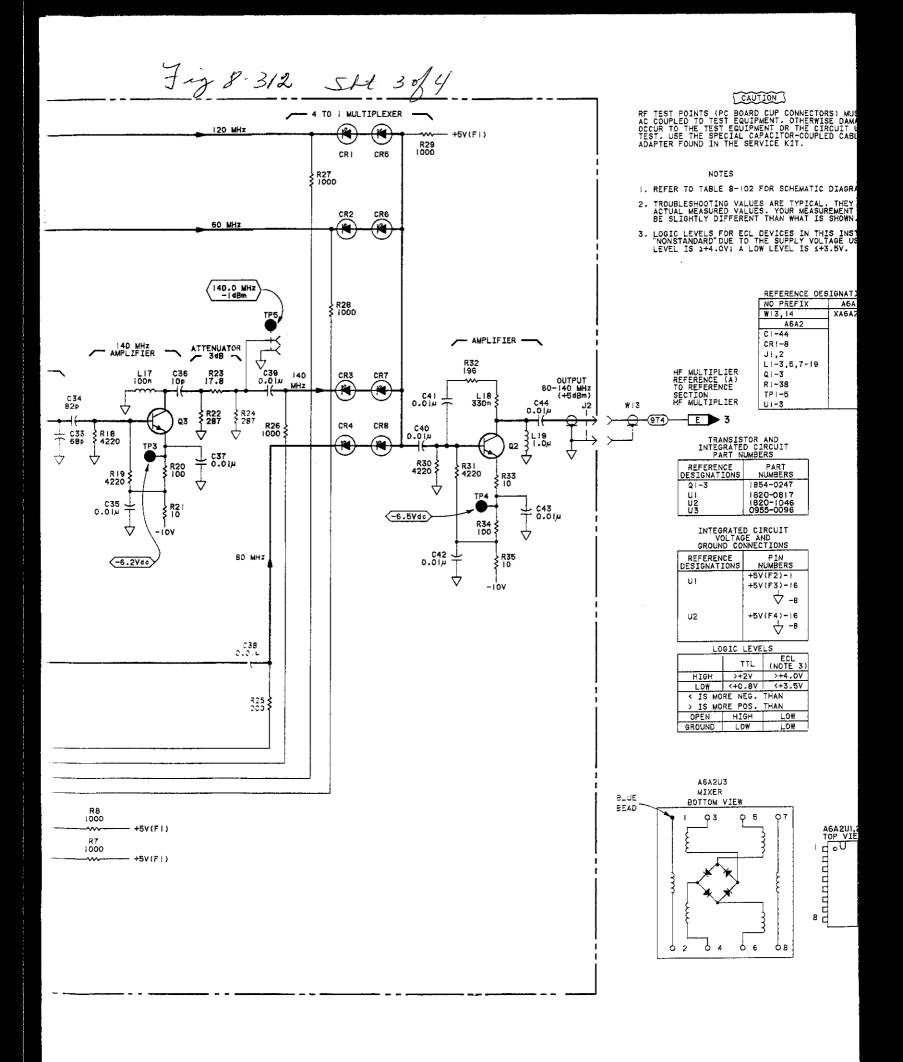

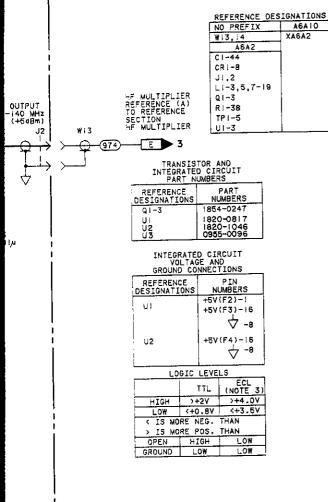

| <b>S</b> S3                             | BD2              | A6A3                | Reference Section HF Multiplier                 | 8-313                                         | 6-125                           |

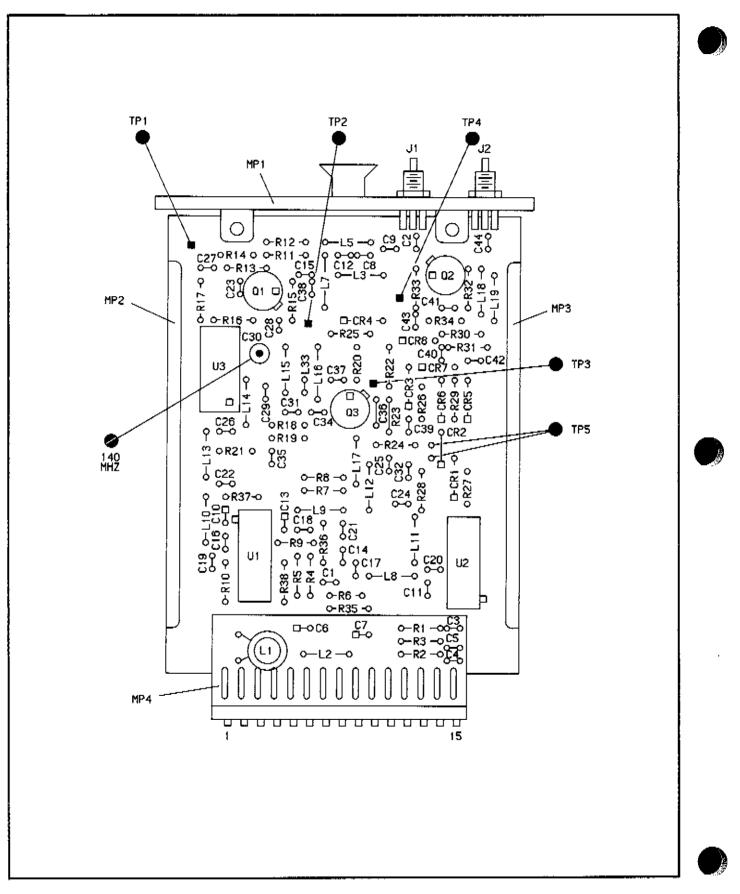

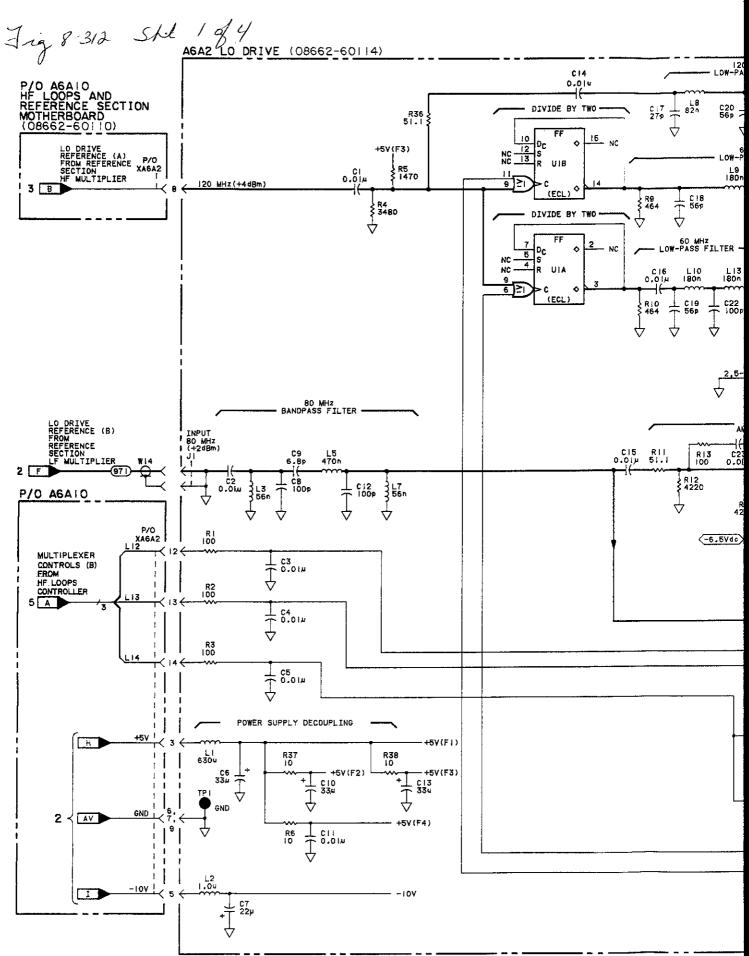

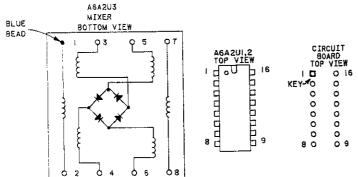

| SS4                                     | BD2              | A6A2                | Reference Section LO Drive                      | 8319                                          | 6-121                           |

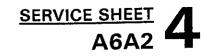

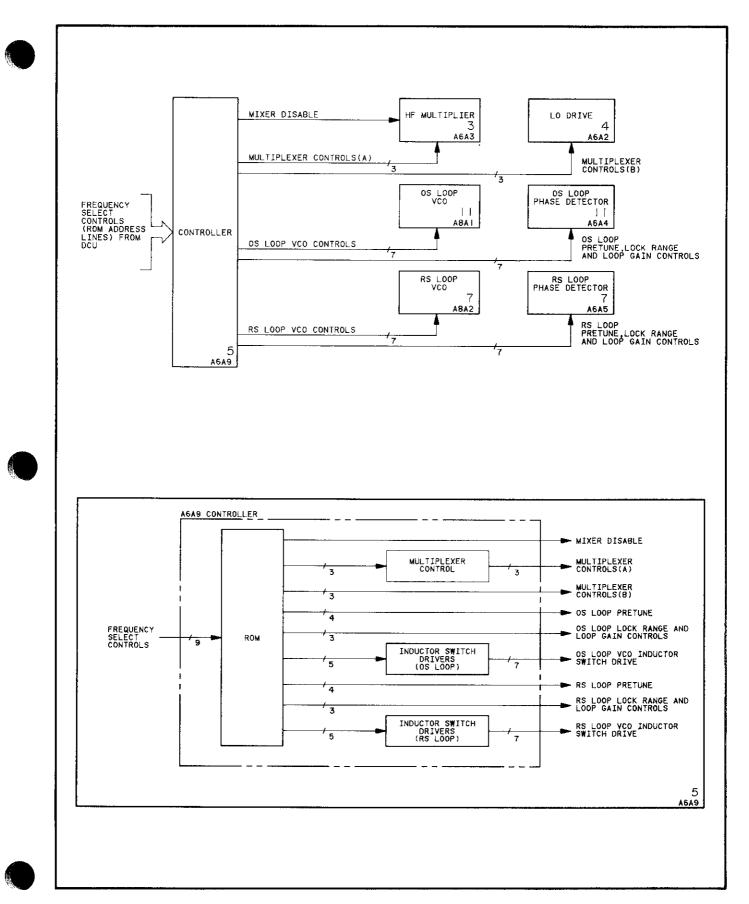

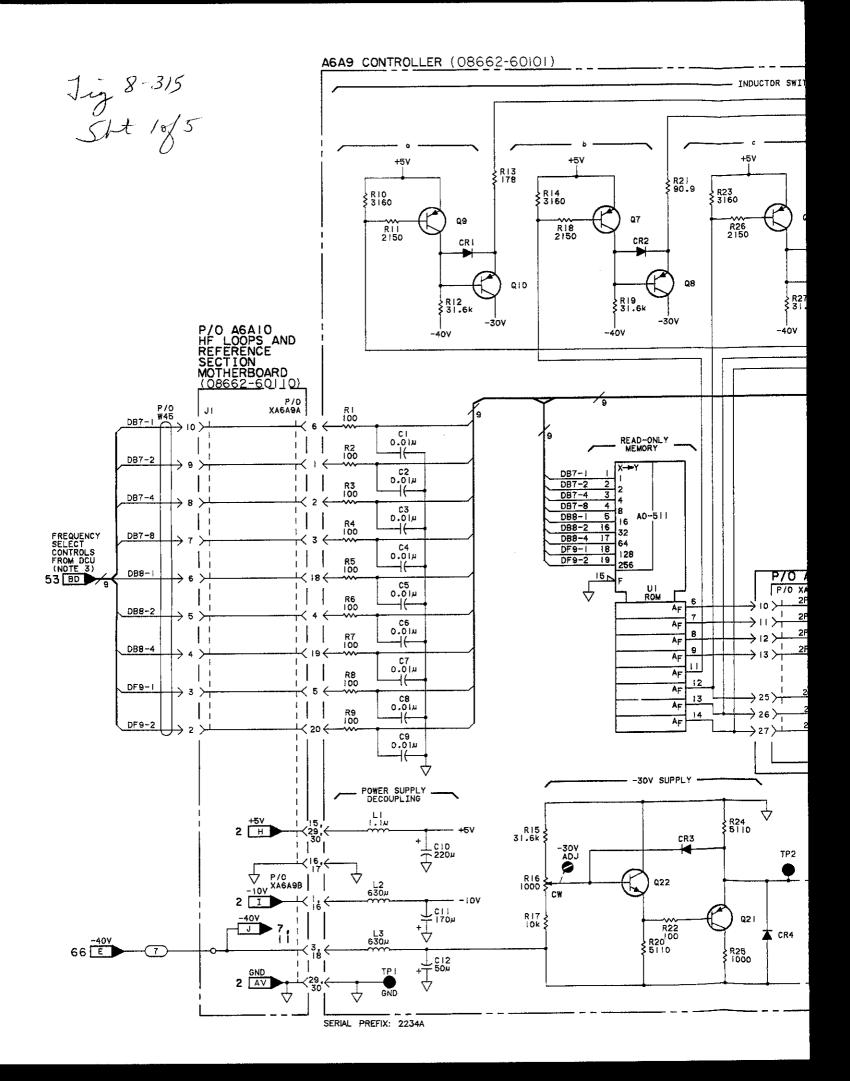

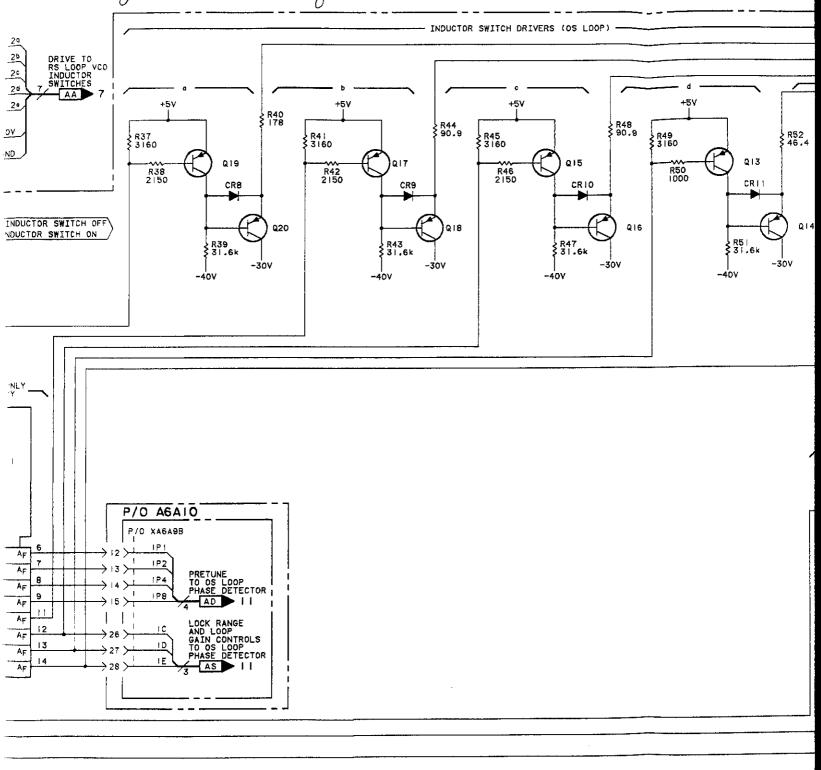

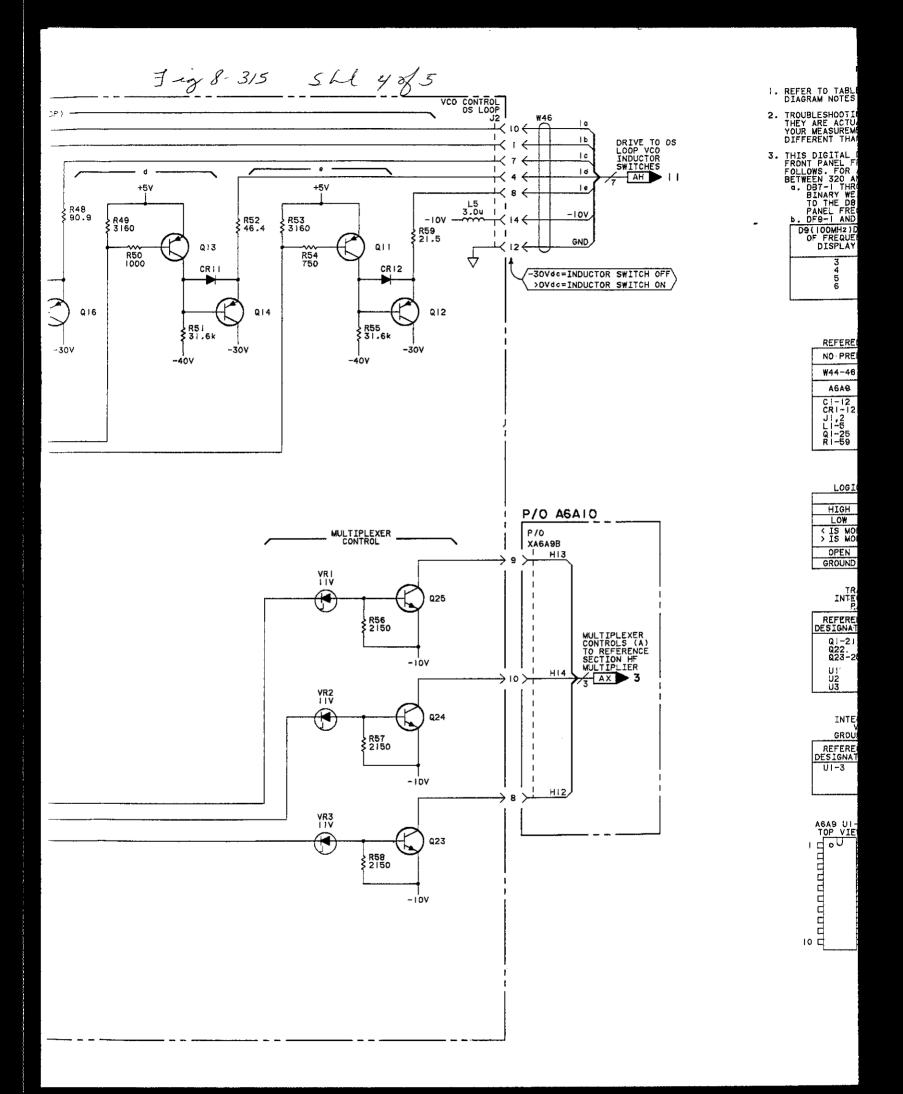

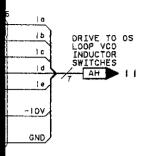

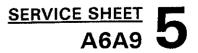

| SS5                                     | BD3              | A6A9                | HP Loops and Reference Sections Controller      | 8-325                                         | 6-155                           |

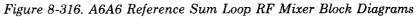

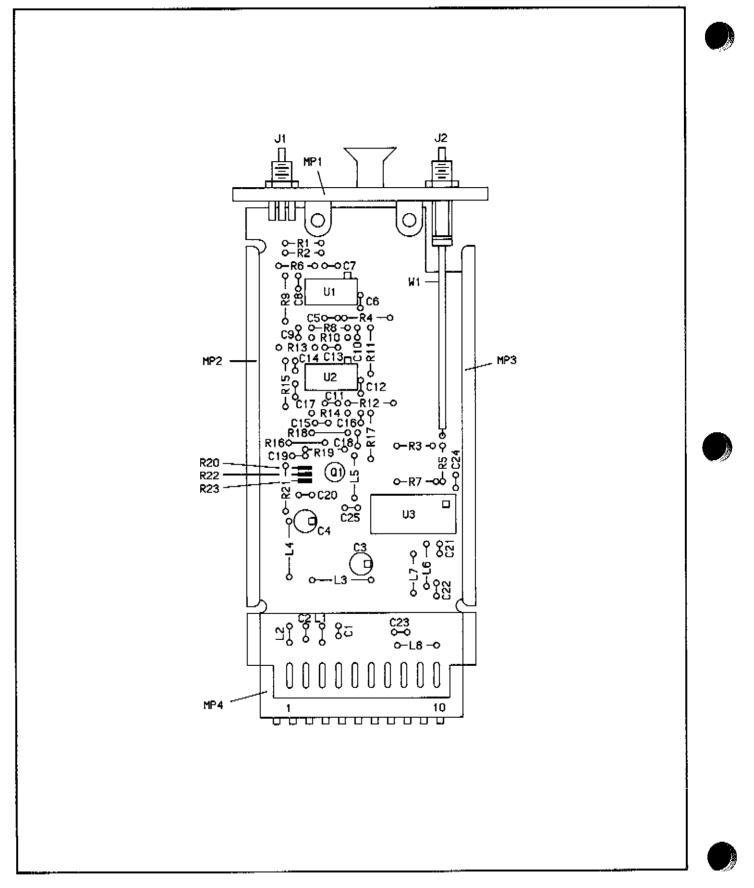

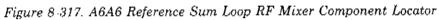

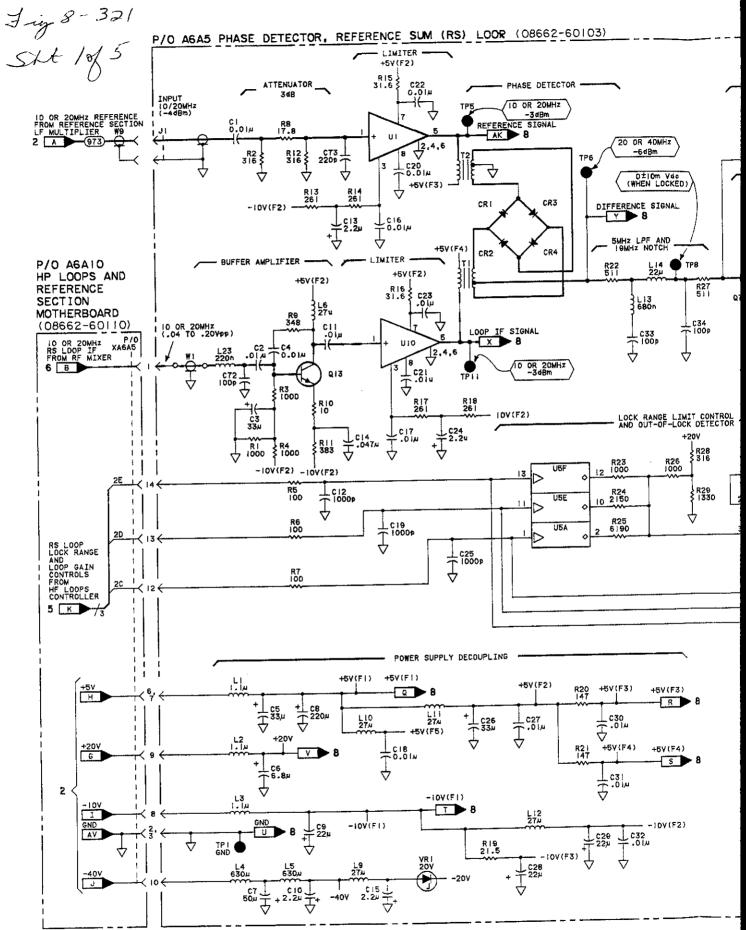

| SS6                                     | 8D3              | A6A6                | Reference Sum Loop RF Mixer                     | 8–331                                         | 6-149                           |

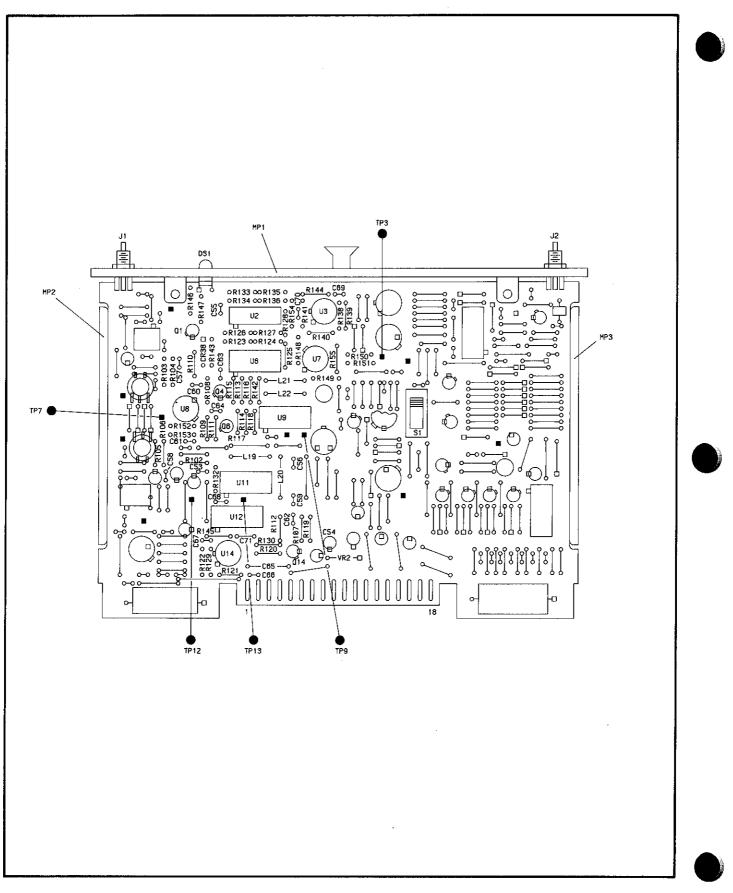

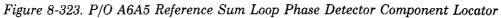

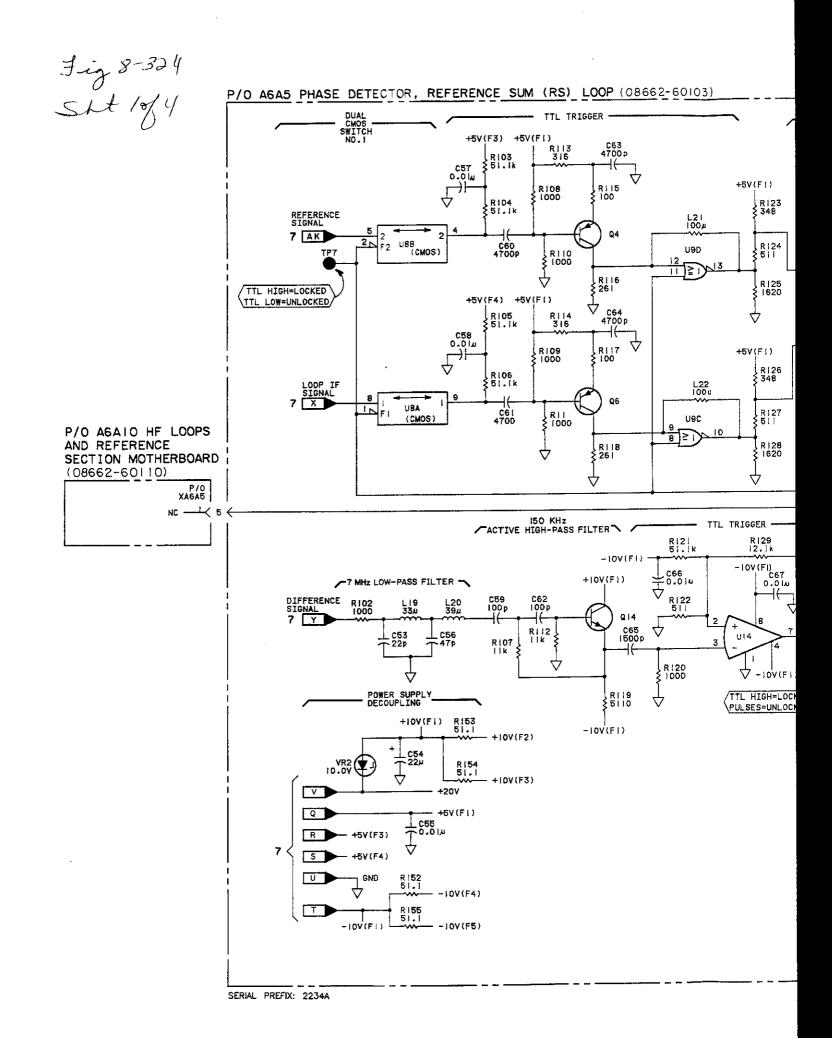

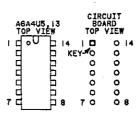

| SS7                                     | BD3              | A6A5                | Reference Sum Loop Phase Detector               | 8-337                                         | 6-133                           |

| SS8                                     | BD3              | A6A5                | Reference Sum Loop Phase Detector               | 8-347                                         | 6-133                           |

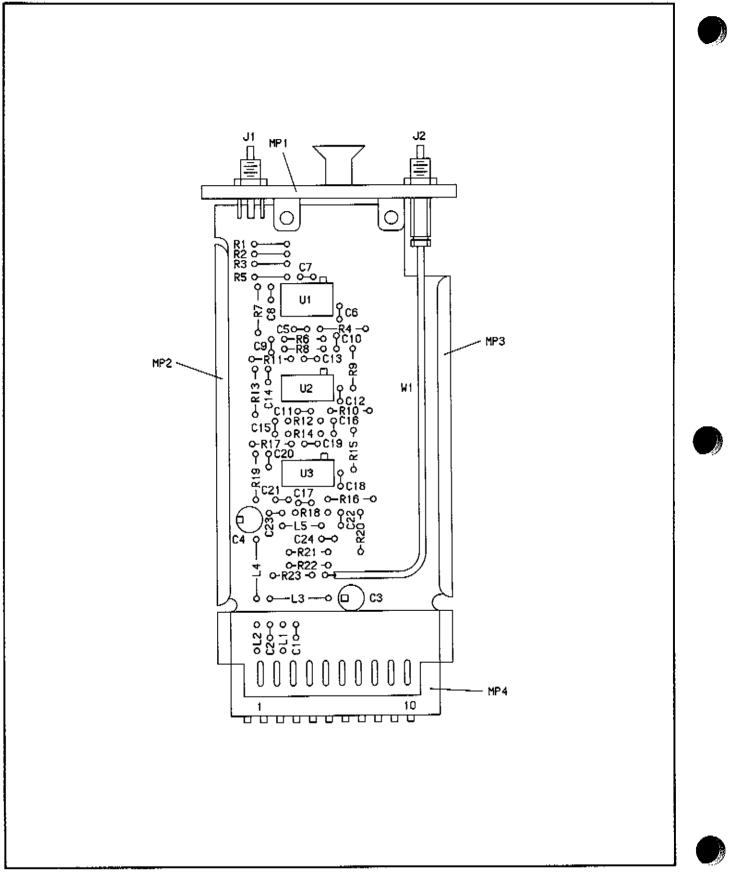

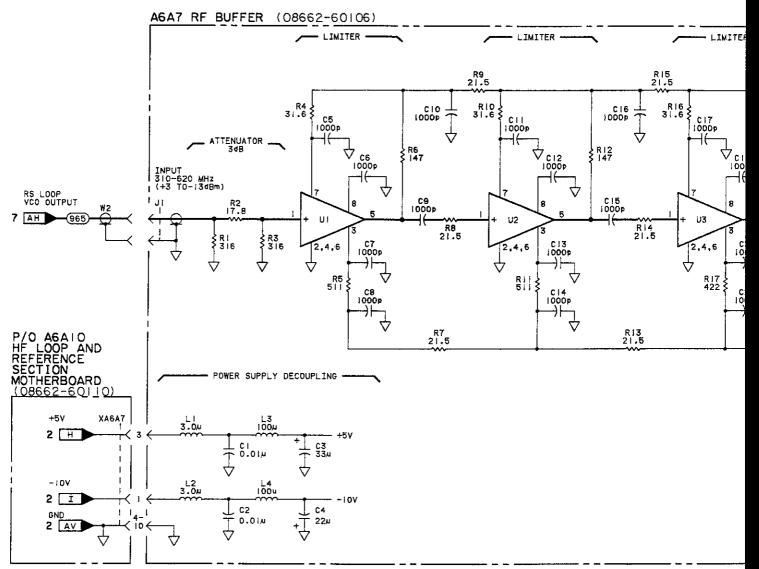

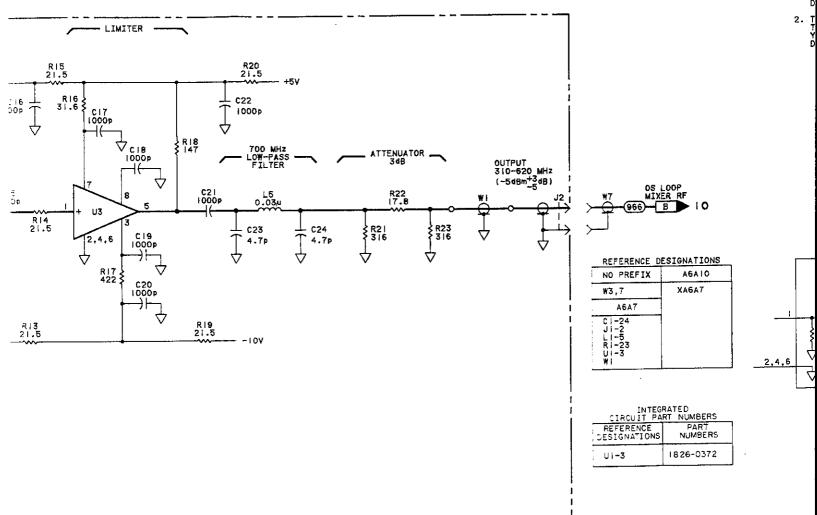

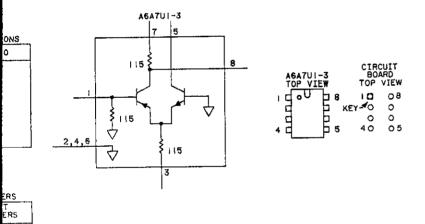

| 559                                     | BD3              | A6A7                | RF Buffer                                       | 8-355                                         | <b>6</b> ⊶151                   |

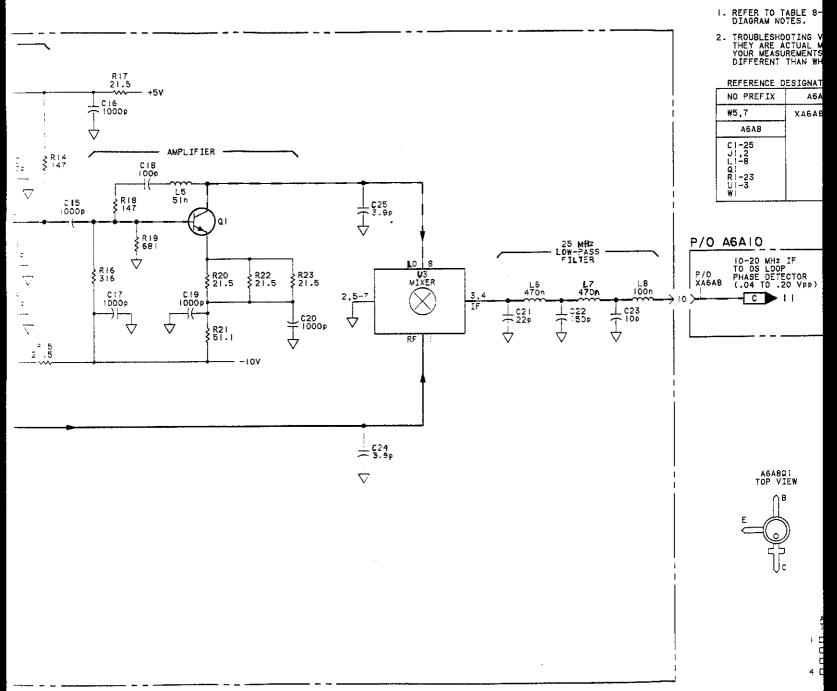

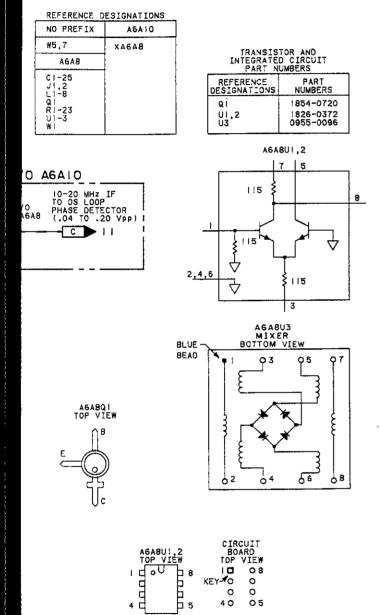

| SS10                                    | BD3              | A6A8                | Output Sum Loop RF Mixer                        | 8361                                          | 6-153                           |

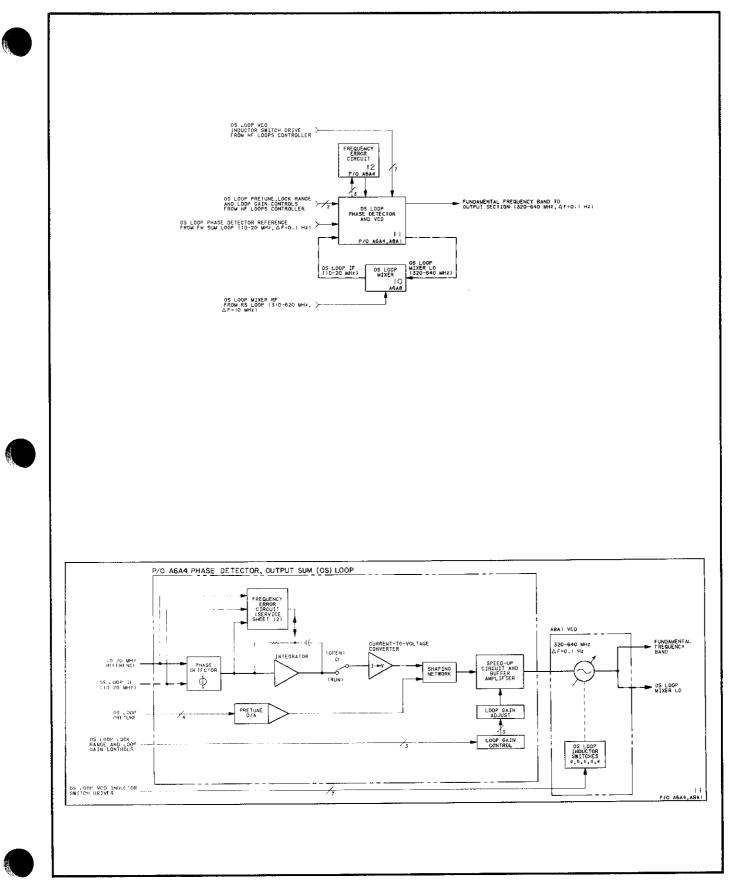

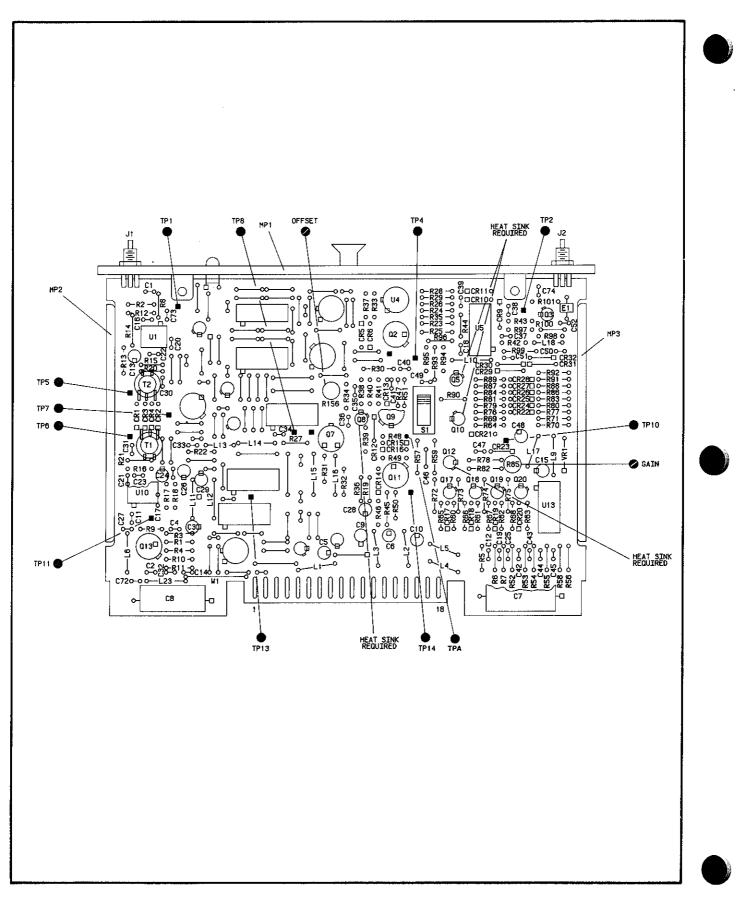

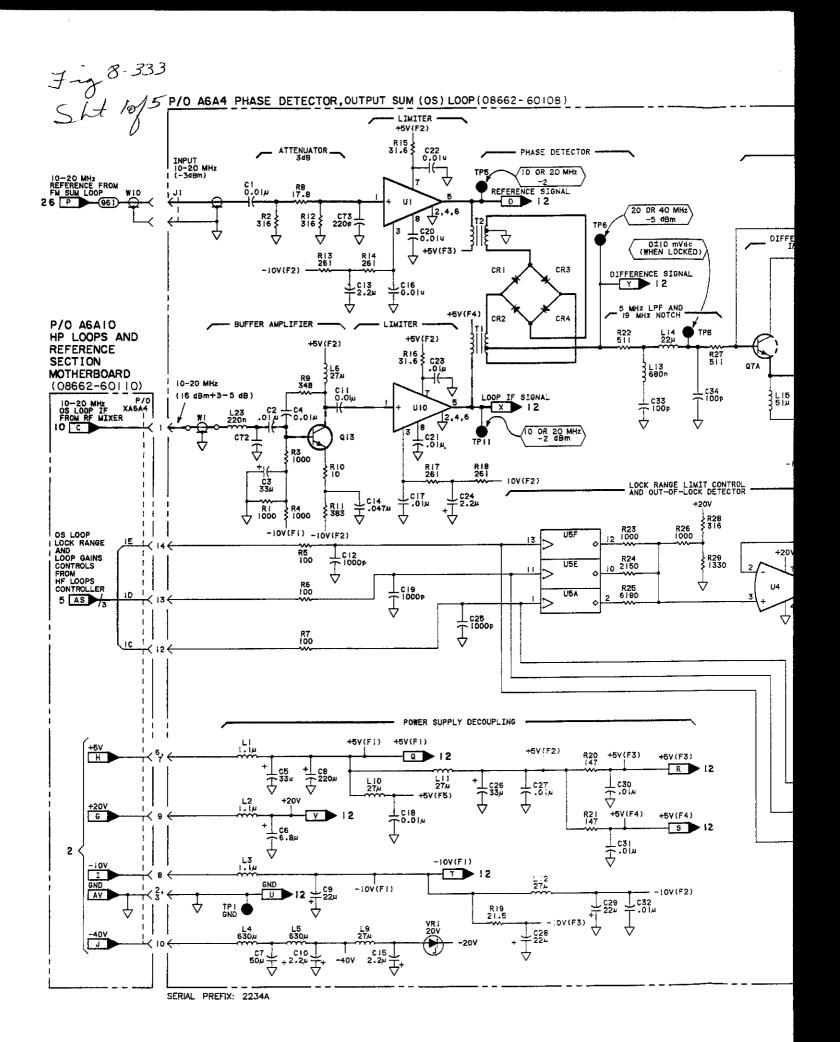

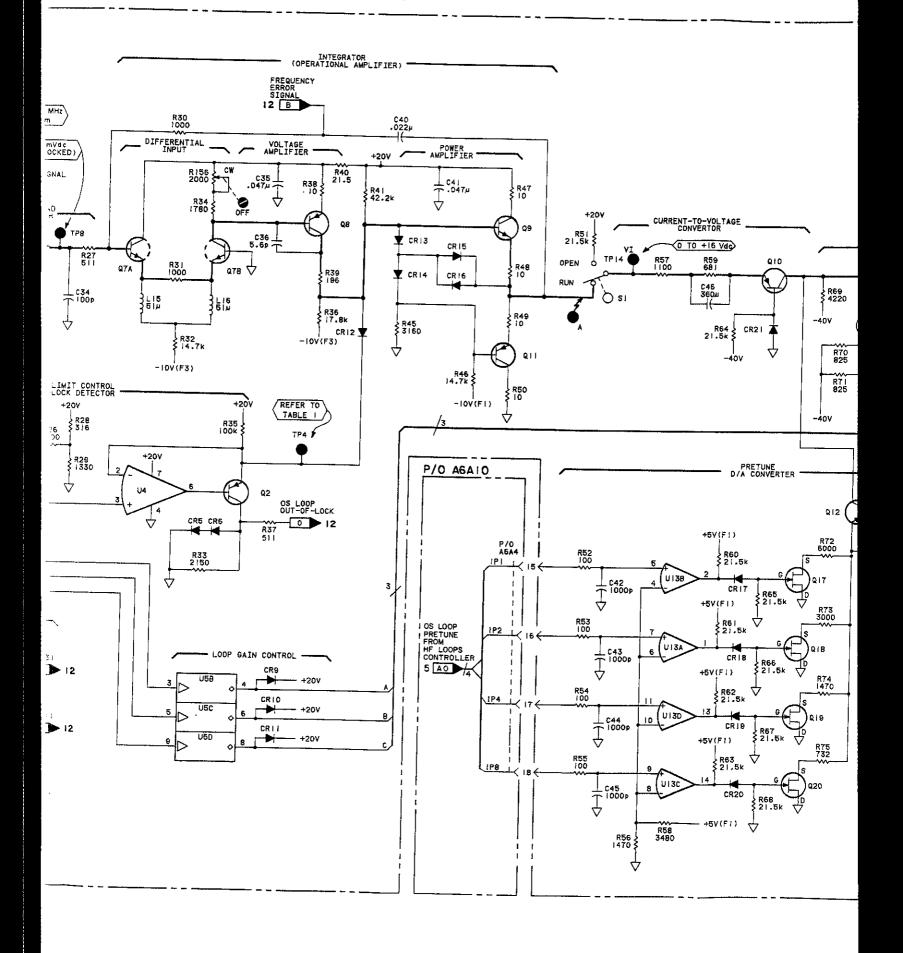

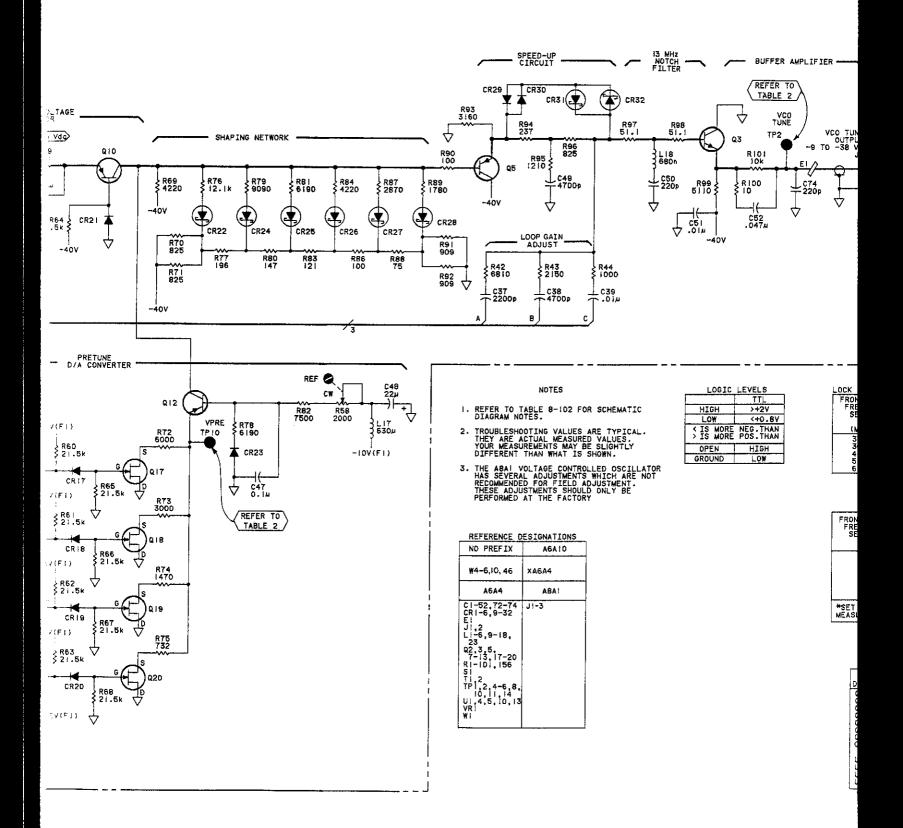

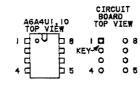

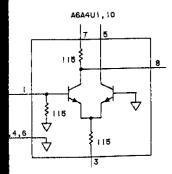

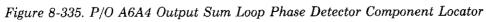

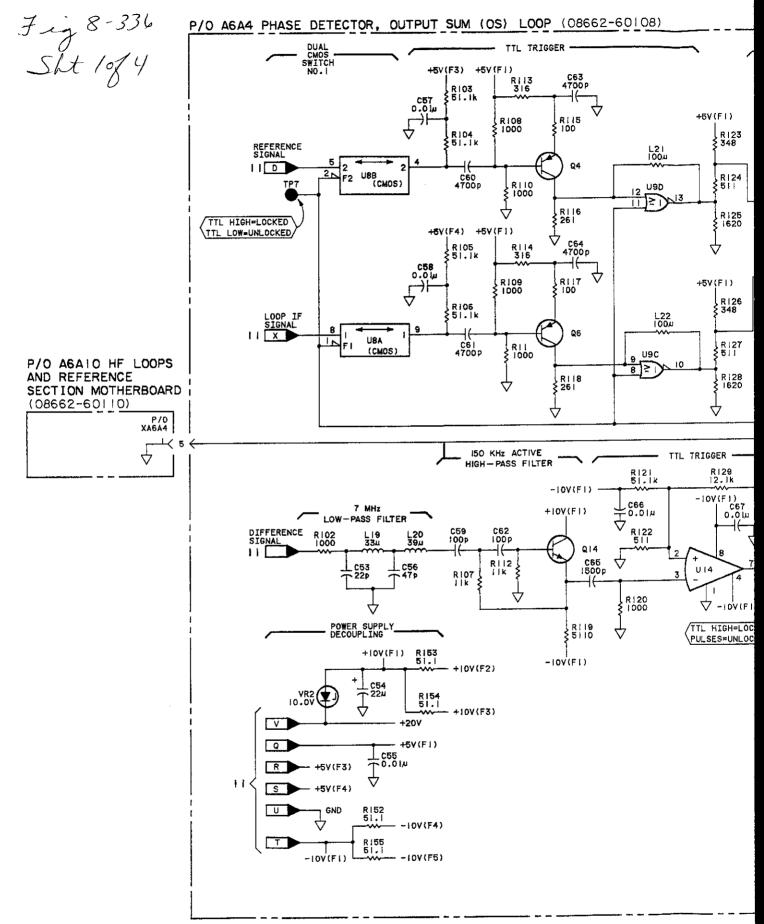

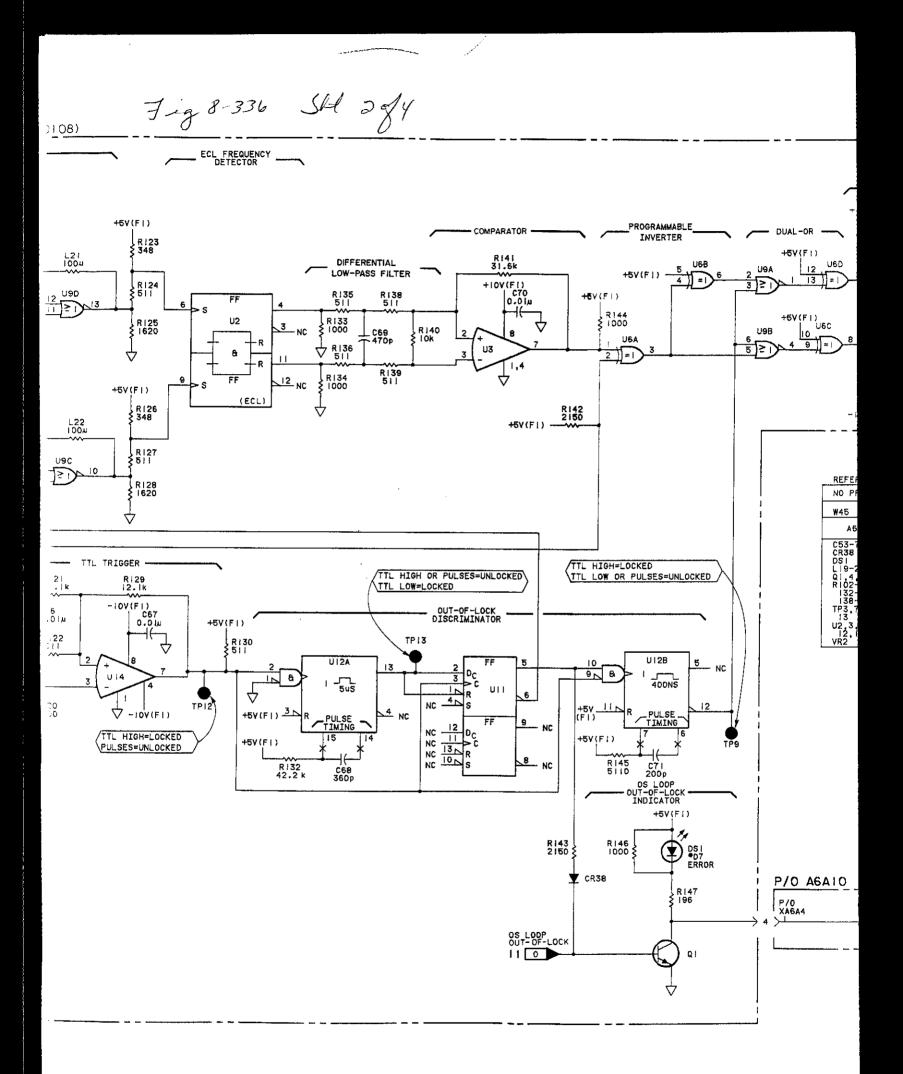

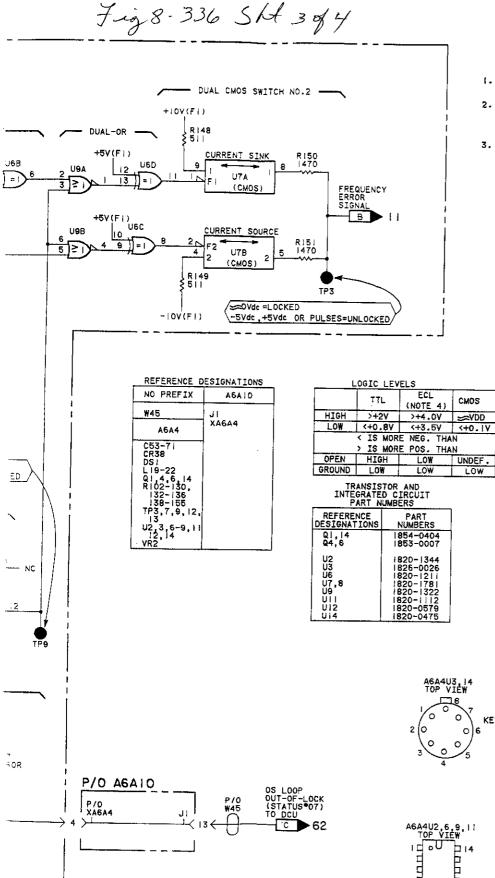

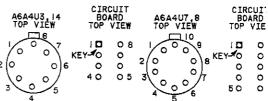

| SS11                                    | BD3              | A6A4                | Output Sum Loop Phase Detector                  | 8–367                                         | 6-133                           |

| SS12                                    | BD3              | A6A4                | Output Sum Loop Phase Detector                  | 8-377                                         | 6–133                           |

•

.

rev.30SEP88

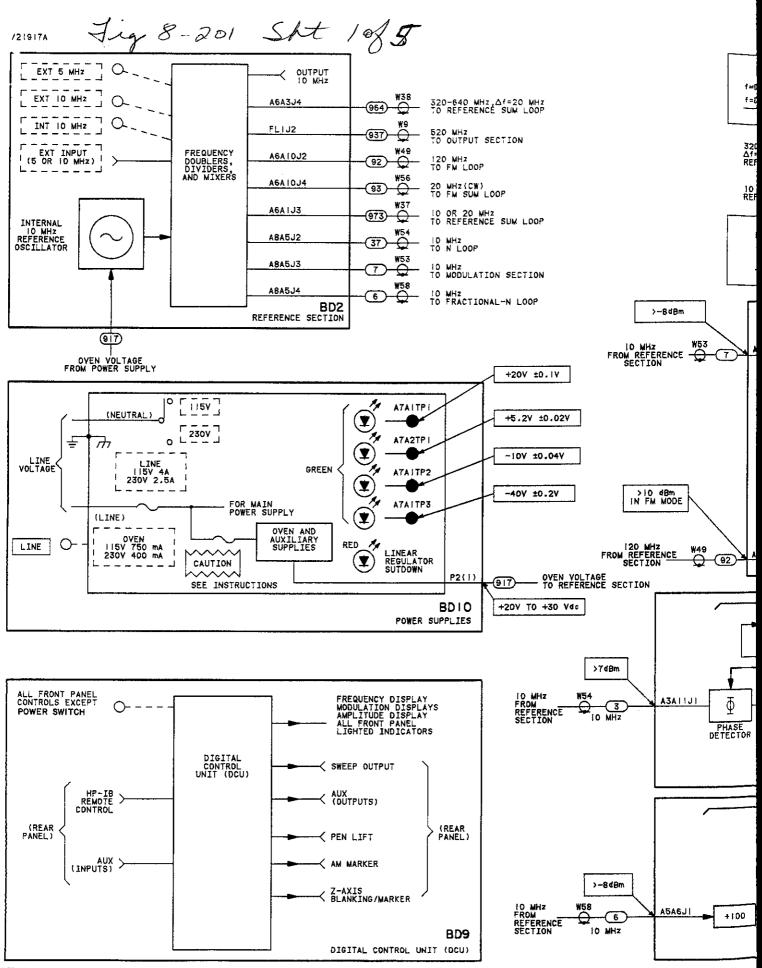

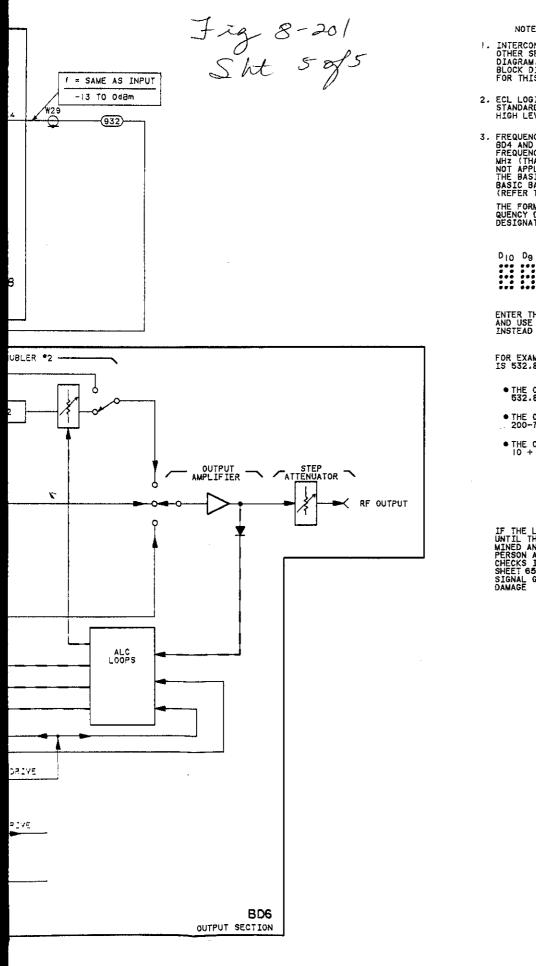

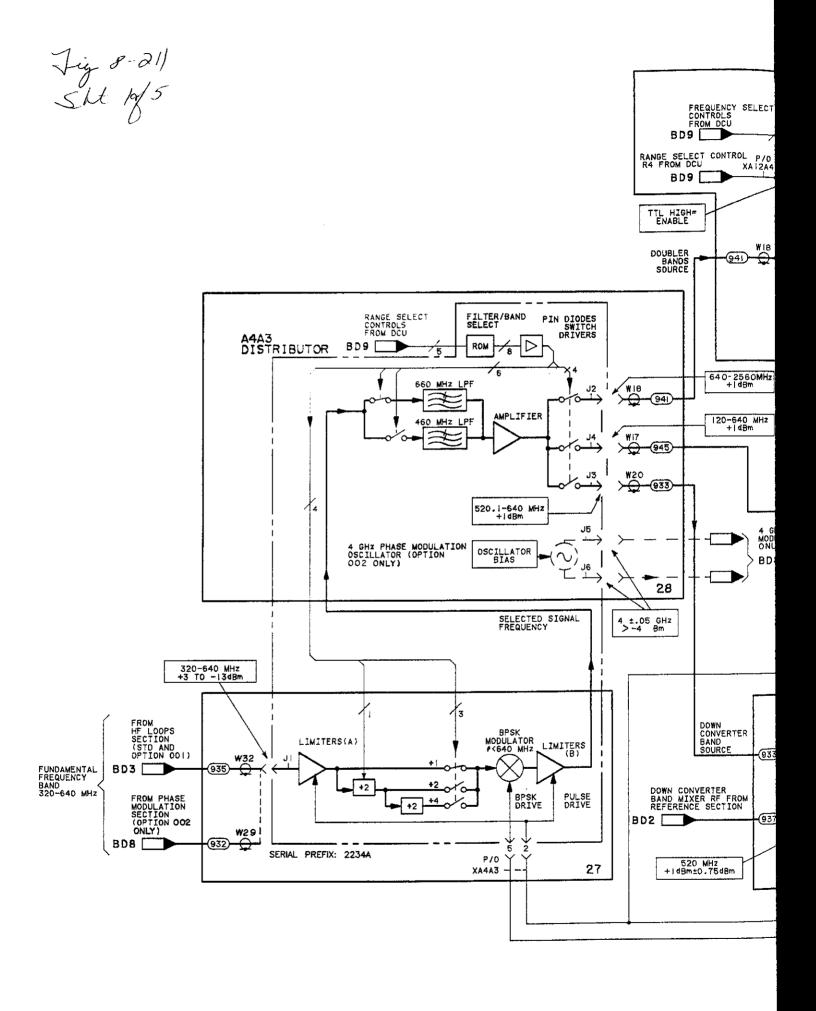

#### SERVICE SHEET BD1 OVERALL BLOCK DIAGRAM

#### **REFERENCE:**

Simplified Operation (Section III) Operator's Checks (Section III) Table 4-1. Recommended Performance Tests After Adjustments or Repairs. Table 5-2. Post-Repair Adjustment Procedures.

#### PRINCIPLES OF OPERATION

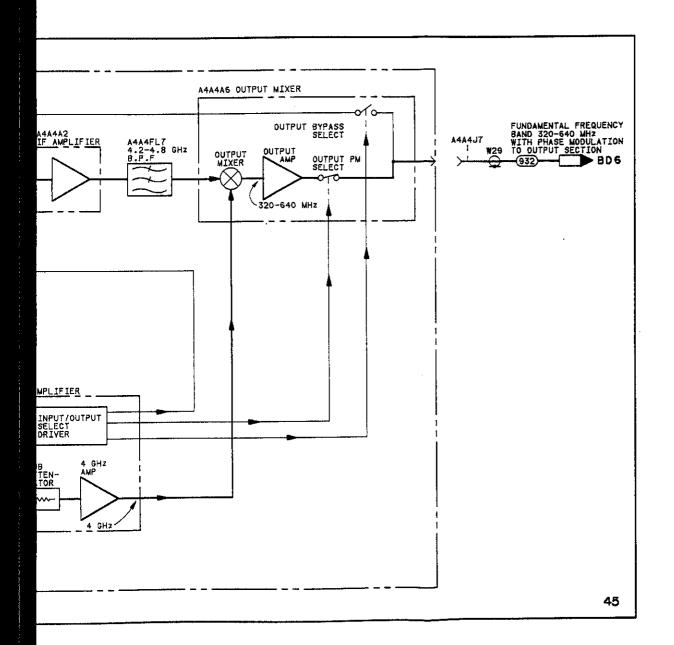

The basic frequency generating circuitry is composed of the Reference Section, phase lock loops and Output Section (in the upper-left, center and right hand portions of the block diagram respectively). All of the reference frequencies used within the instrument are obtained from the Reference Section. A total of seven phase lock loops work together to produce the fundamental frequency band of 320 to 640 MHz with a step resolution of 0.1 Hz. This fundamental (or basic) band is sent to the Output Section where it is doubled, passed straight through or down-converted to produce the entire frequency range at the RF output (.1 to 2560 MHz).

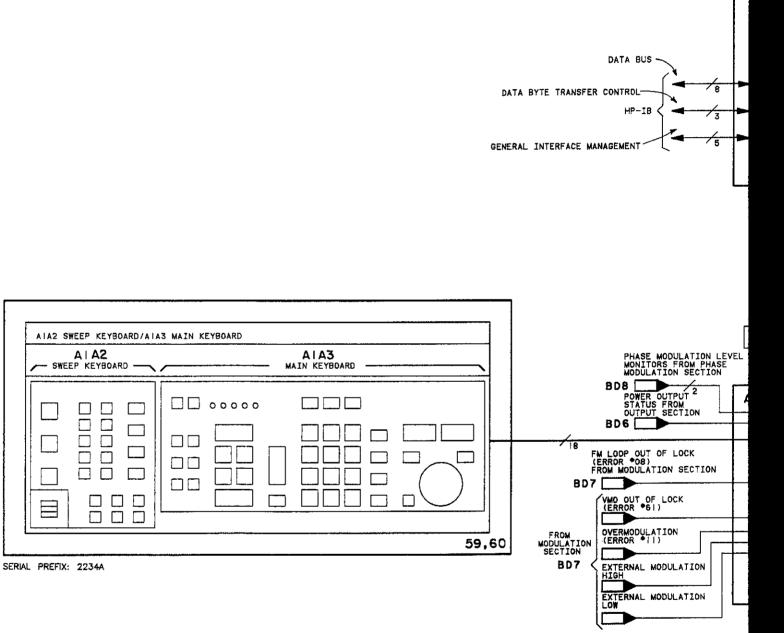

The Digital Control Unit (DCU) controls the operation of the unit. It accepts keyboard or remote inputs and generates internal data and control signals to control the signal at the RF output. Power for the instrument is supplied by a switching-regulated power supply.

#### Reference Section

All of the reference frequencies used within the instrument are obtained from the Reference Section. This block is composed of doublers, dividers, and mixers, all of which are driven by a single temperaturestabilized 10 MHz crystal oscillator. Outputs from the Reference Section are 10, 20, 120, 520, and 320-640 MHz (in 20 MHz steps). Signal levels vary depending on which section they are being sent to.

#### Phase Lock Loops

The Generator uses the indirect synthesis method for generating output frequencies. Phase lock loop (PLL) circuits are locked to signals from the Reference Section and generate signals which are combined to give the desired output frequency. All output frequencies retain the same accuracy and stability as the 10 MHz reference signal. PLL's are found in the High Frequency, Low Frequency, Fractional-N, and Modulation Sections.

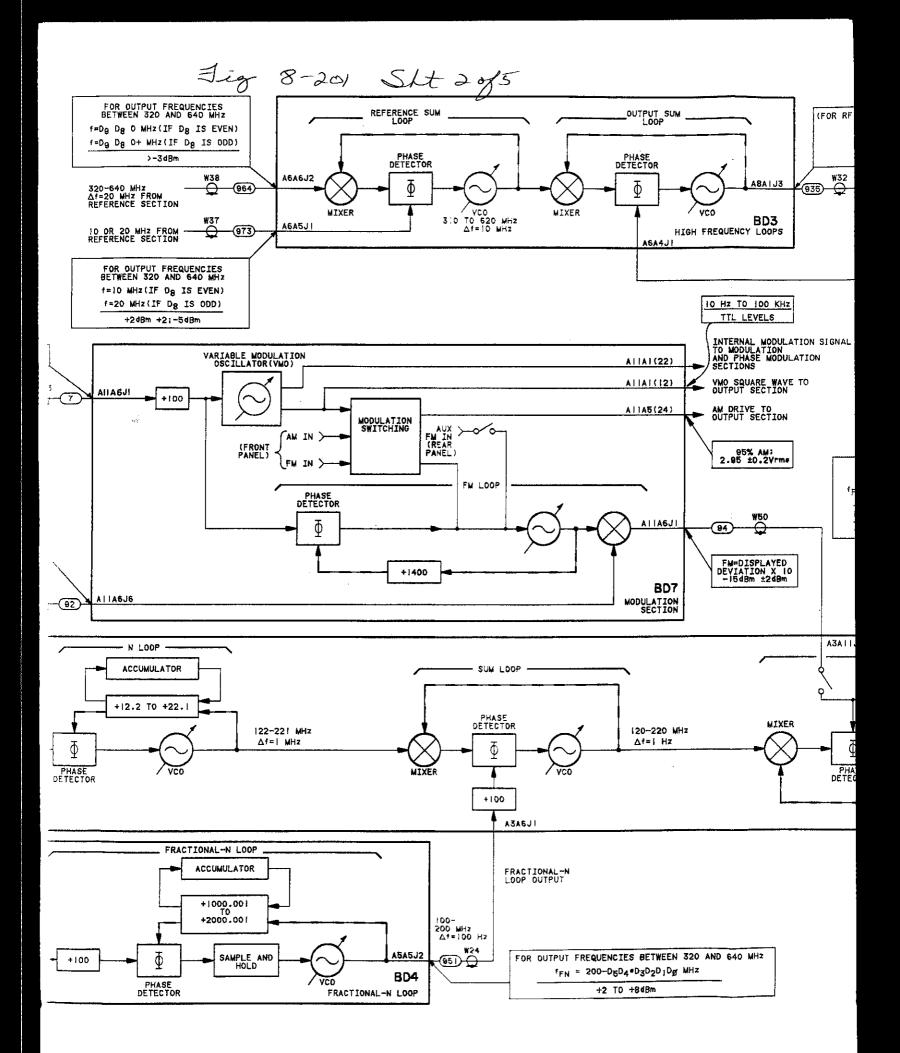

#### High Frequency Loops

The Reference Sum Loop and the Output Sum Loop are two nearly identical circuits. The Reference Sum Loop starts with 320-640 MHz and 10 or 20 MHz signals from the Reference Section. Together, these signals are related to digits D9 and D8 in the FREQUENCY readout (in the basic band only). These signals are combined in the Output Sum Loop with the low frequency loops output that has a 0.1 Hz resolution.

#### Low Frequency Loops

The Low Frequency section consolidates several signals and produces an output signal having the characteristics of all of the inputs. This section has three phase lock loops: the N-Loop, the Low Frequency Sum Loop, and the FM Sum Loop.

The N-Loop generates a signal related to the D7 and D6 digits of the FREQUENCY readout (in the basic band). The other two loops combine this signal with outputs from the Fractional-N Loop. A 20 MHz signal is frequency modulated at the level needed to provide the desired amount of deviation at the front panel RF output.

#### Fractional-N-Loop

The Fractional-N-Loop uses the 10 MHz reference signal to produce an output that is related to digits D5, D4, D3, D2, D1, and D0 of the FREQUENCY readout (in the 320-640 MHz "basic band"). The phase lock loop is called "Fractional-N" because the divider in the feedback circuit can divide by both integer and fractional values. This is accomplished by using digital dividers that by themselves only divide by integer values, but with extra control circuitry can switch the "divide-by" integer (N) between two values so that the average value of N contains a fractional part.

For example, to divide by 1300.455, the divider would divide by 1301 for 455 cycles and by 1300 for 545 cycles. Over 1000 cycles, the effective division is by 1300.455. The Fractional-N-Loop provides high resolution, fast switching, and low noise.

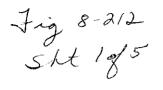

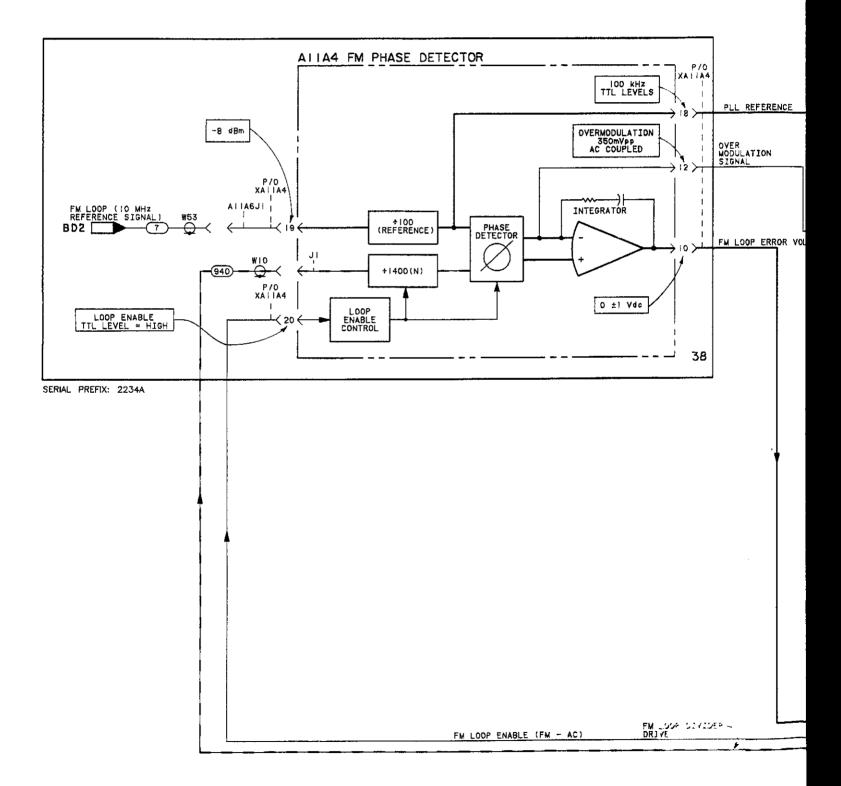

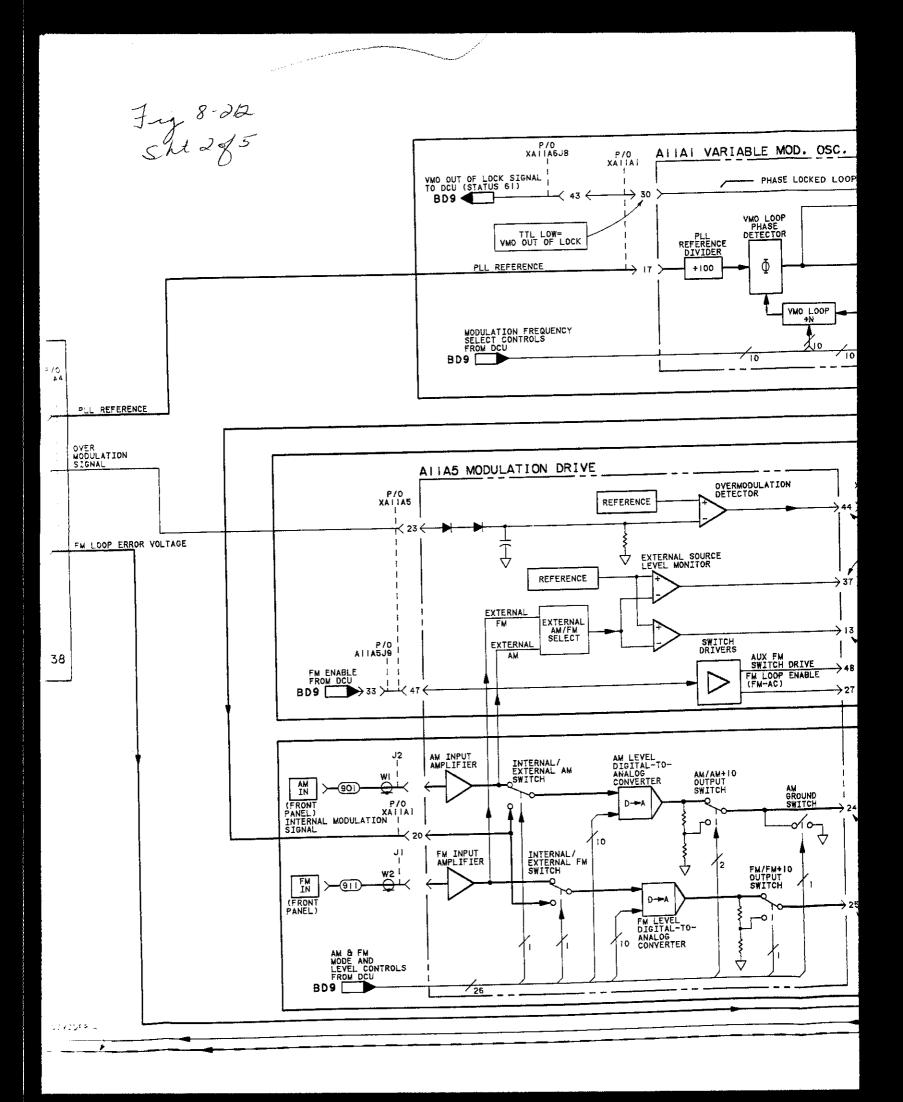

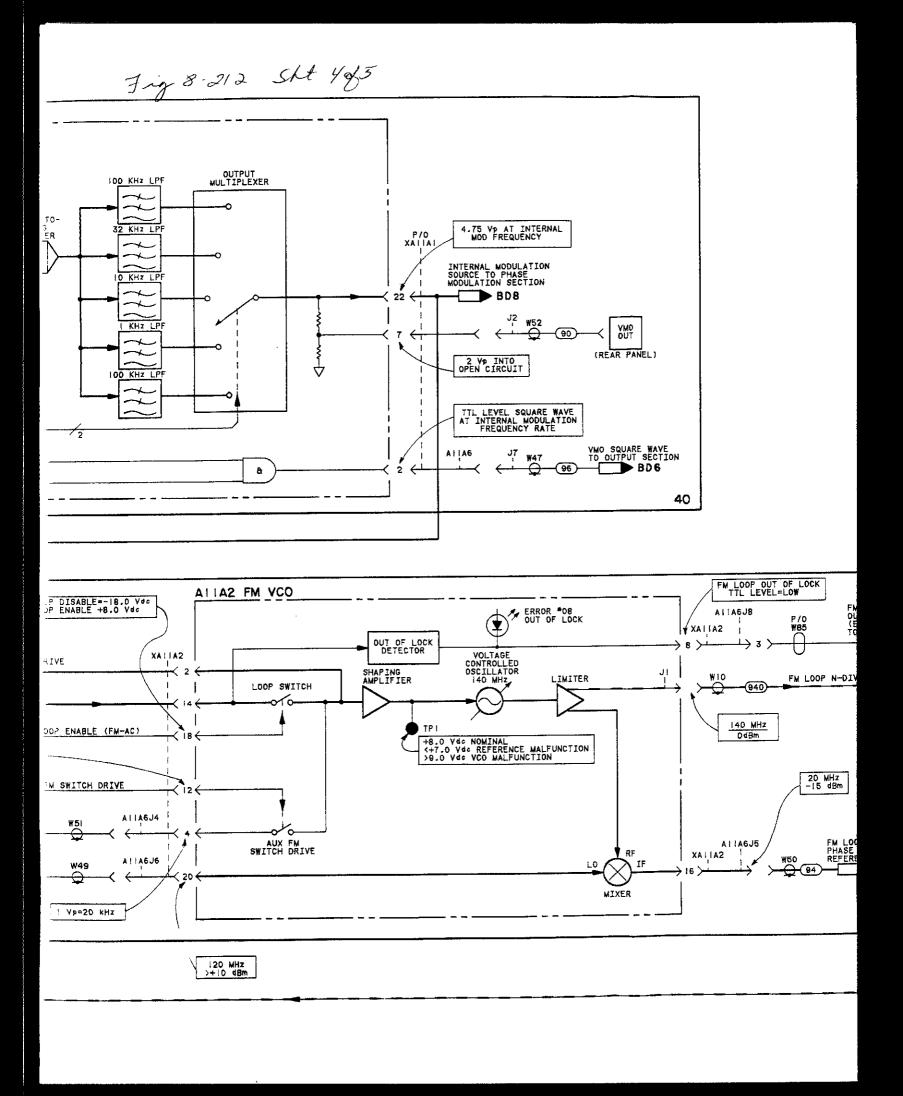

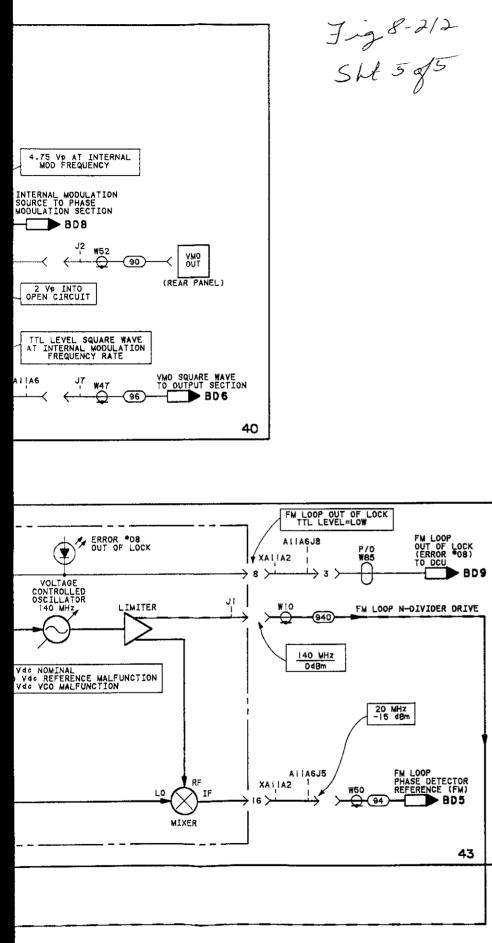

#### Modulation Section and FM Loop

The Modulation Section has a Variable Modulation Oscillator (VMO) that produces modulation source signals at rates from 10.0 Hz to 99.9 kHz with 3 digit resolution. External modulating signals can be applied to the front panel AM IN, FM IN, and PM IN connectors. Simultaneous modulation is possible.

The FM Loop produces one of the reference signals for the FM Sum Loop. The signal is 20 MHz with FM. The phase lock loop is unlocked when a dc-coupled signal from the front panel's FM INPUT is selected. Thus, the 140 MHz Oscillator operates in a free run condition without any correction.

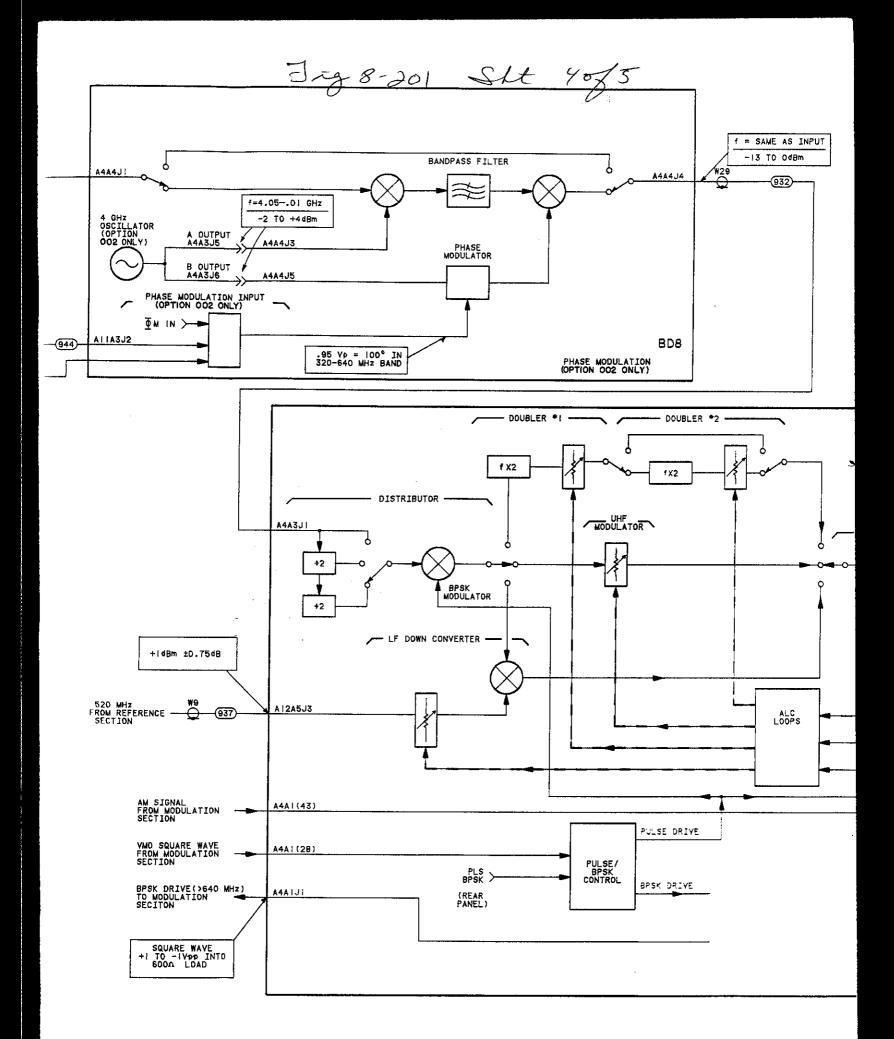

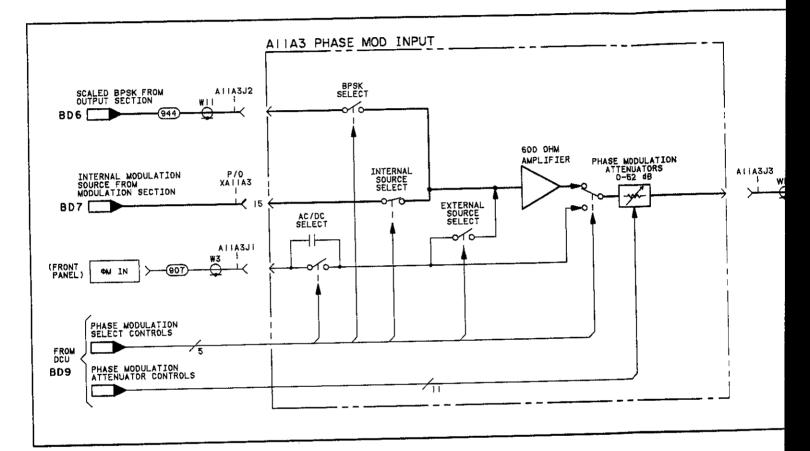

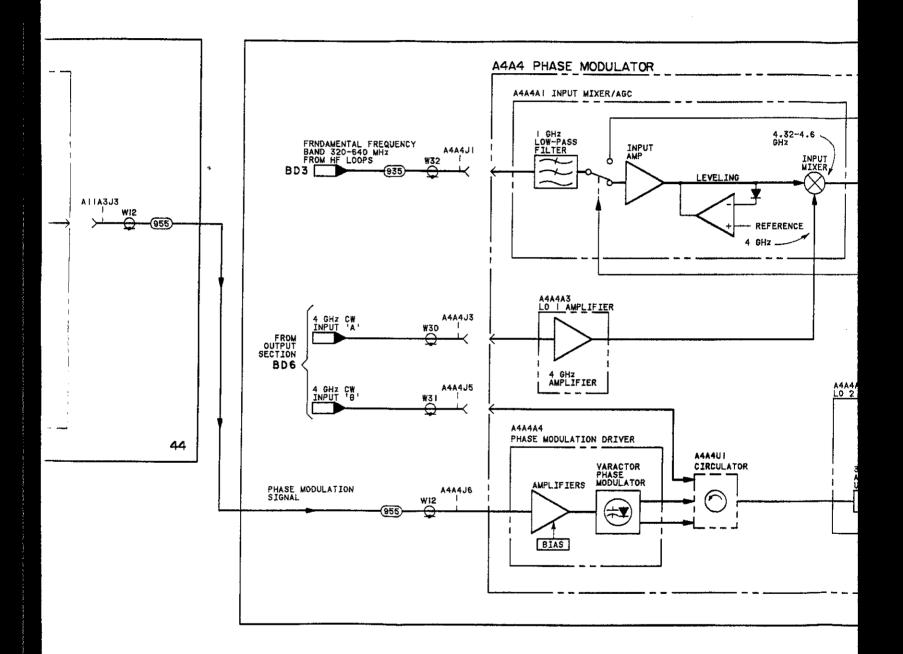

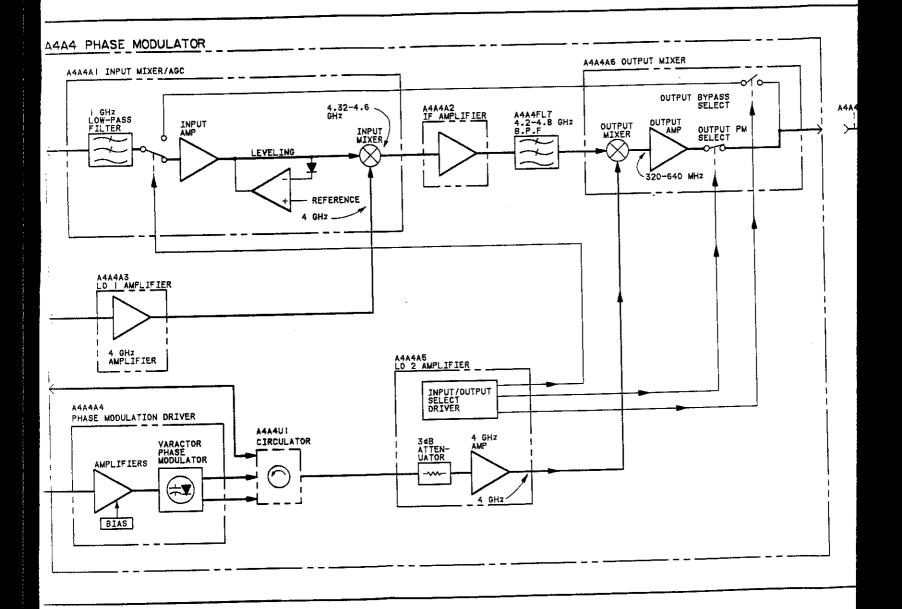

#### Phase Modulation Section (Option 002 Only)

The Phase Modulation section provides phase modulation at up to 10 MHz rates from an external source. BPSK at RF output frequencies of 640 MHz and above are generated in this section.

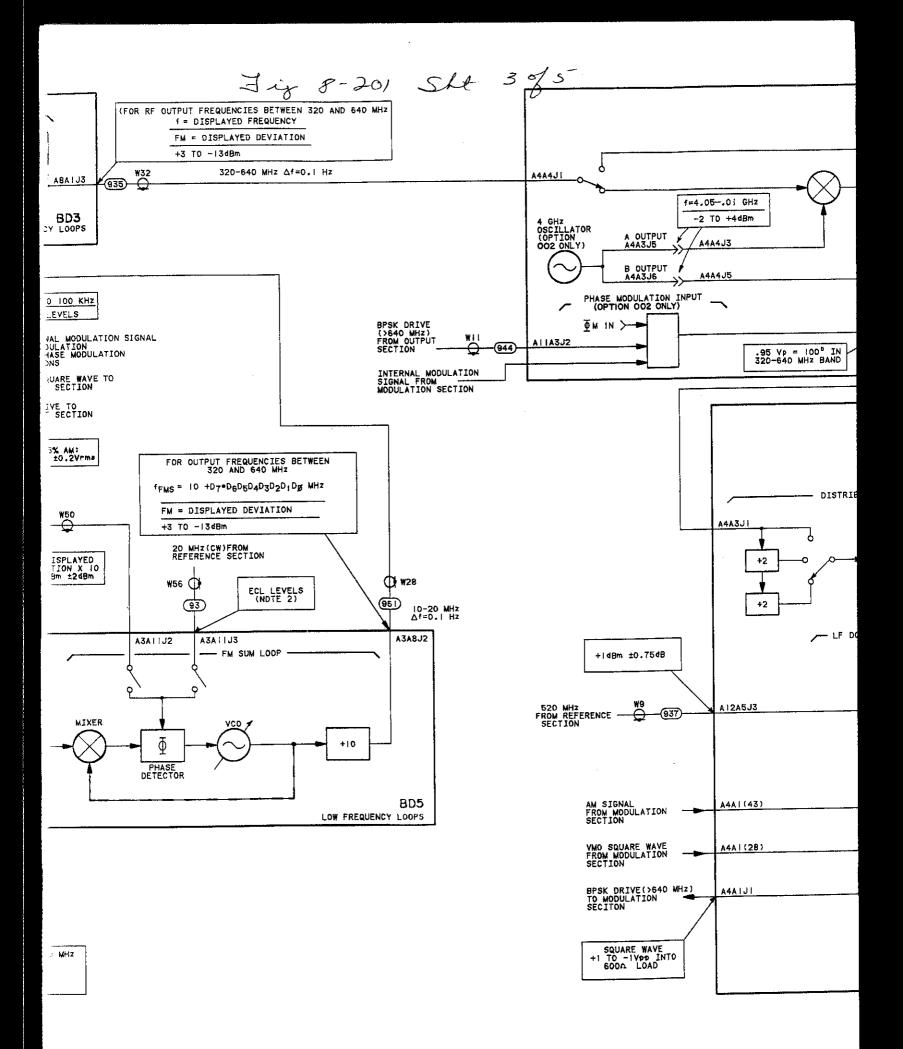

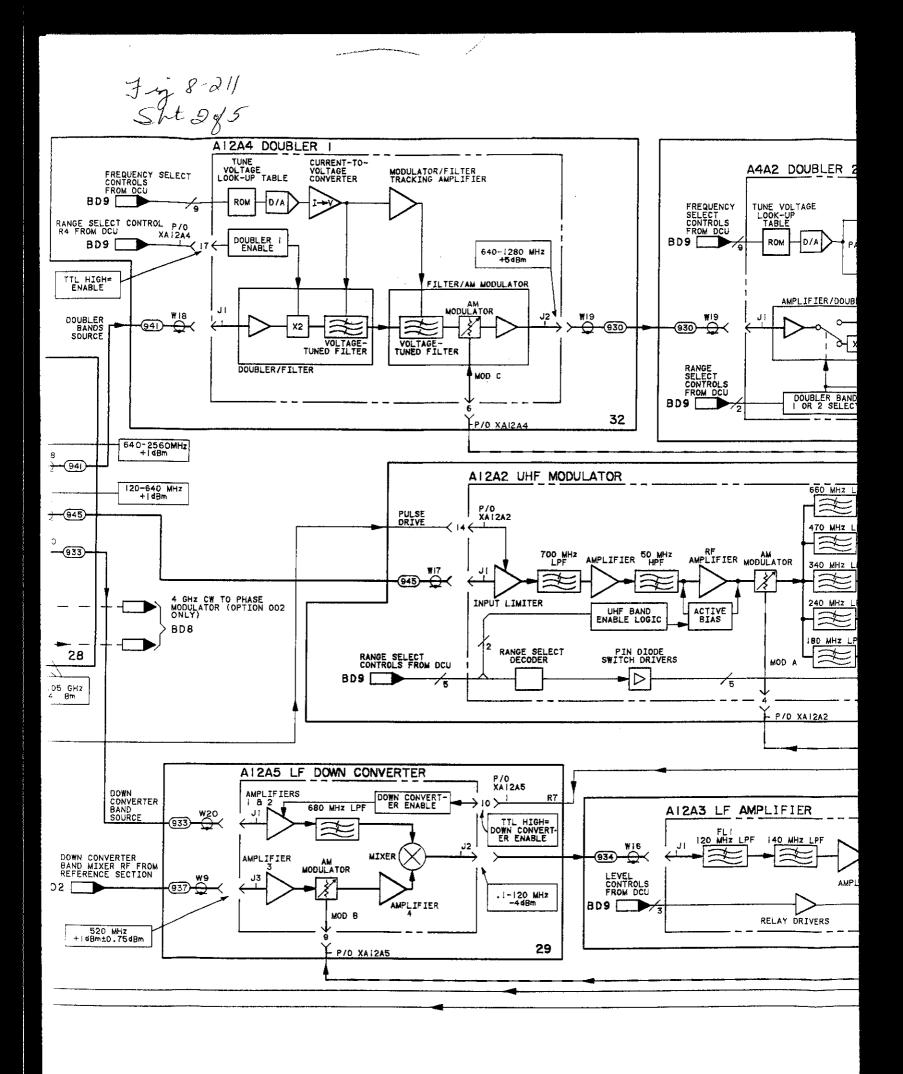

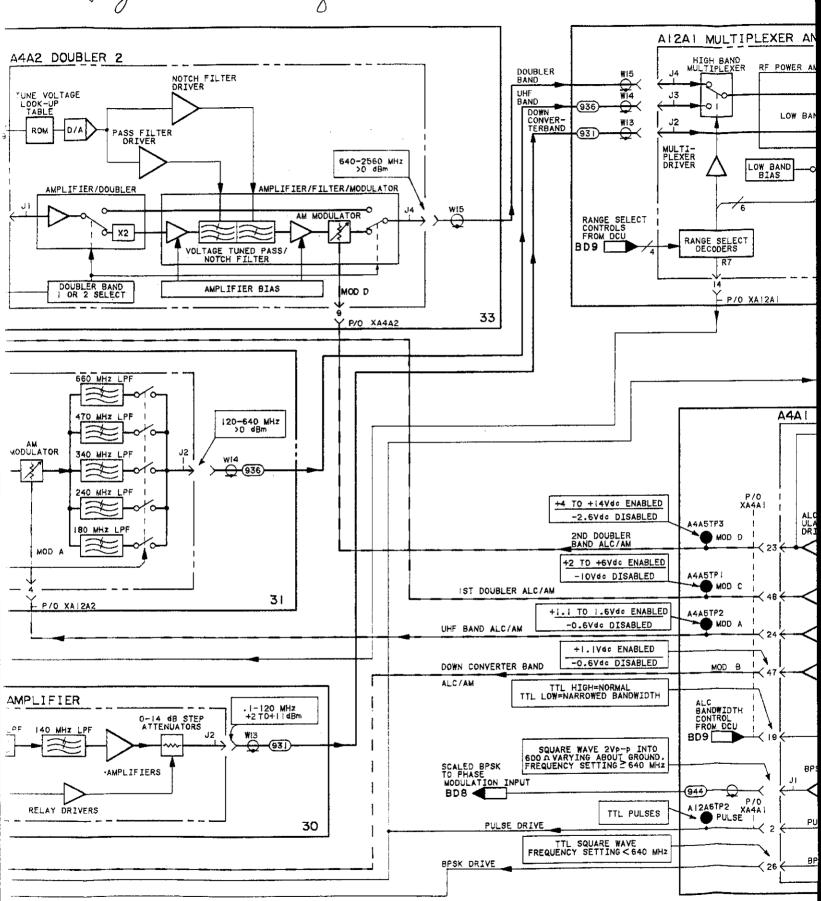

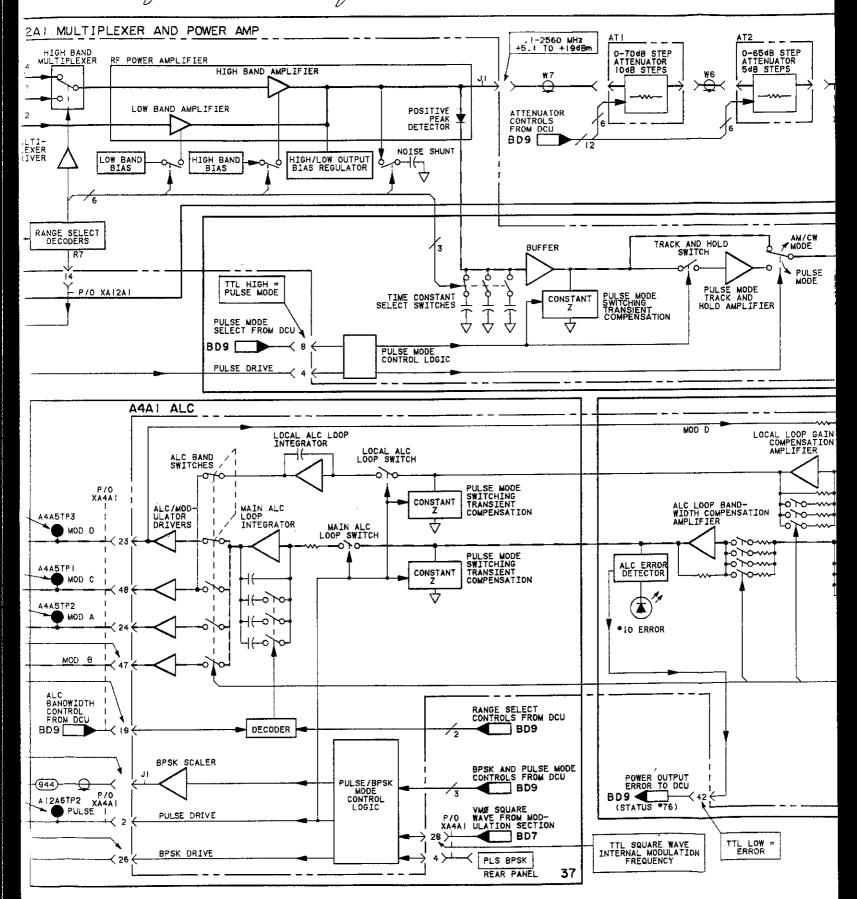

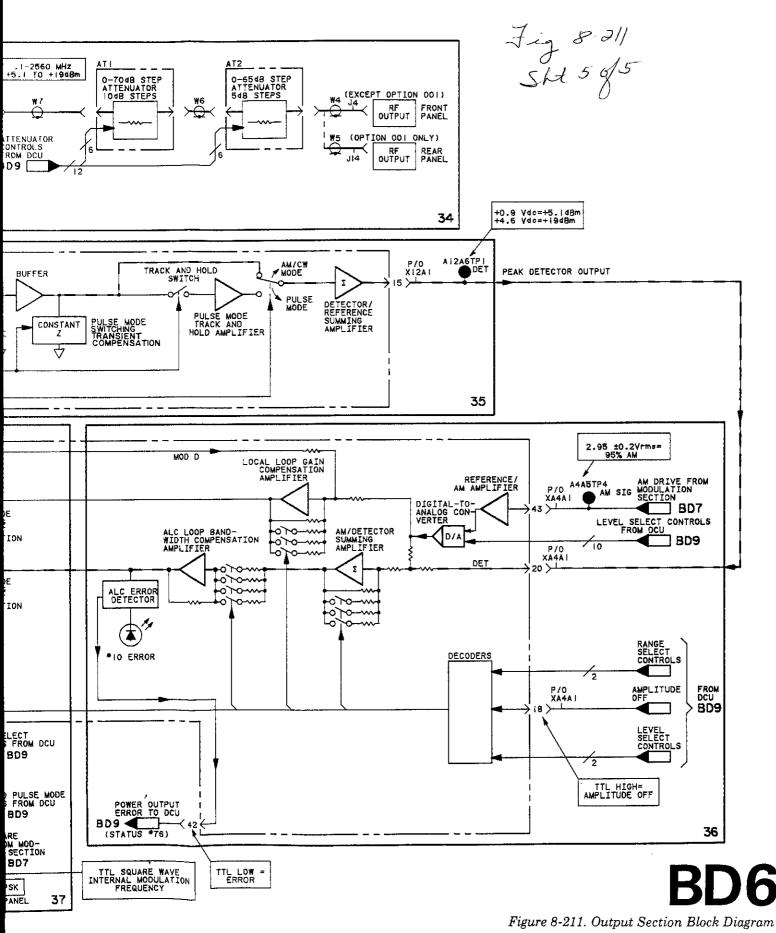

#### Output Section

The output section converts the basic band (320 to 640 MHz) from the High Frequency Section to all other frequencies by multiplying it, passing it through, or dividing it. This section also controls the RF level of the signal. It does this with a group of electromechanical attenuators. These attenuators reduce the amplitude in 5 dB increments from 5 dB through 140 dB. Electronic leveling keeps the output level constant and provides finer output step resolution.

Pulse modulation, AM, and BPSK (RF output frequencies < 640 MHz) are generated in the output section.

#### Digital Control Unit

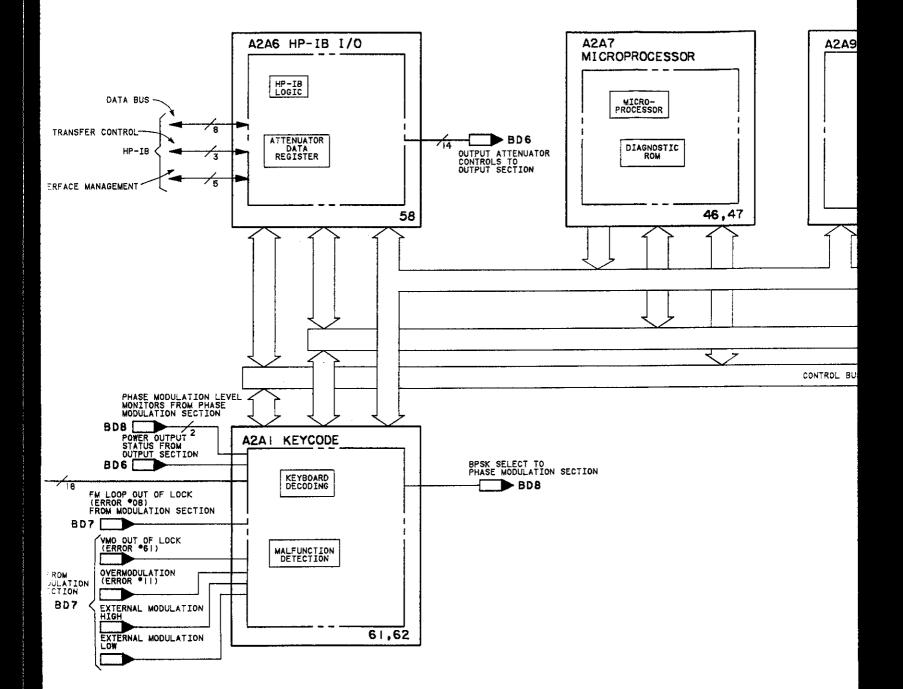

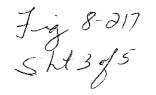

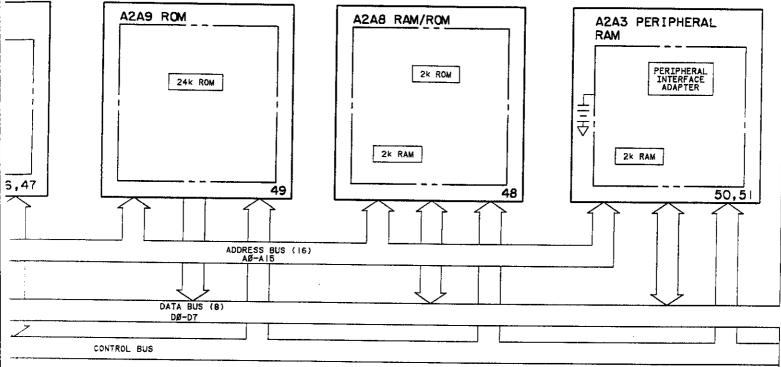

The Digital Control Unit (DCU) is a microprocessor based controller that is responsible for directing the operation of the instrument. It takes information from the keyboard, HP-IB interface or AUX connector. It stores data, calculates the required oscillator frequencies, determines internal switch settings, and exercises general control over the instrument. Although not shown on this block diagram, the DCU is a transfer point for digital data to all the sections.

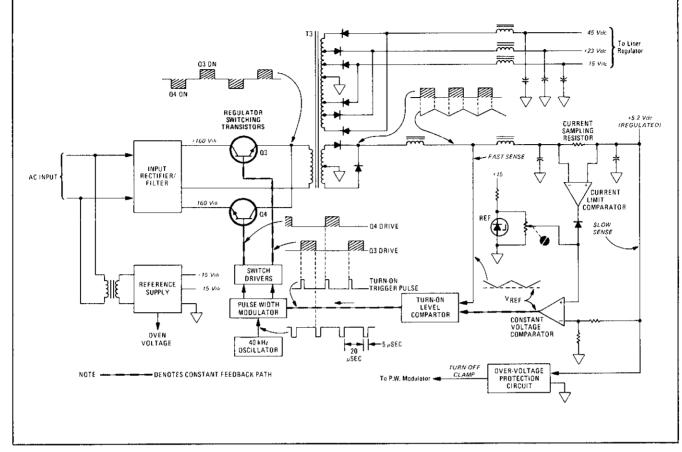

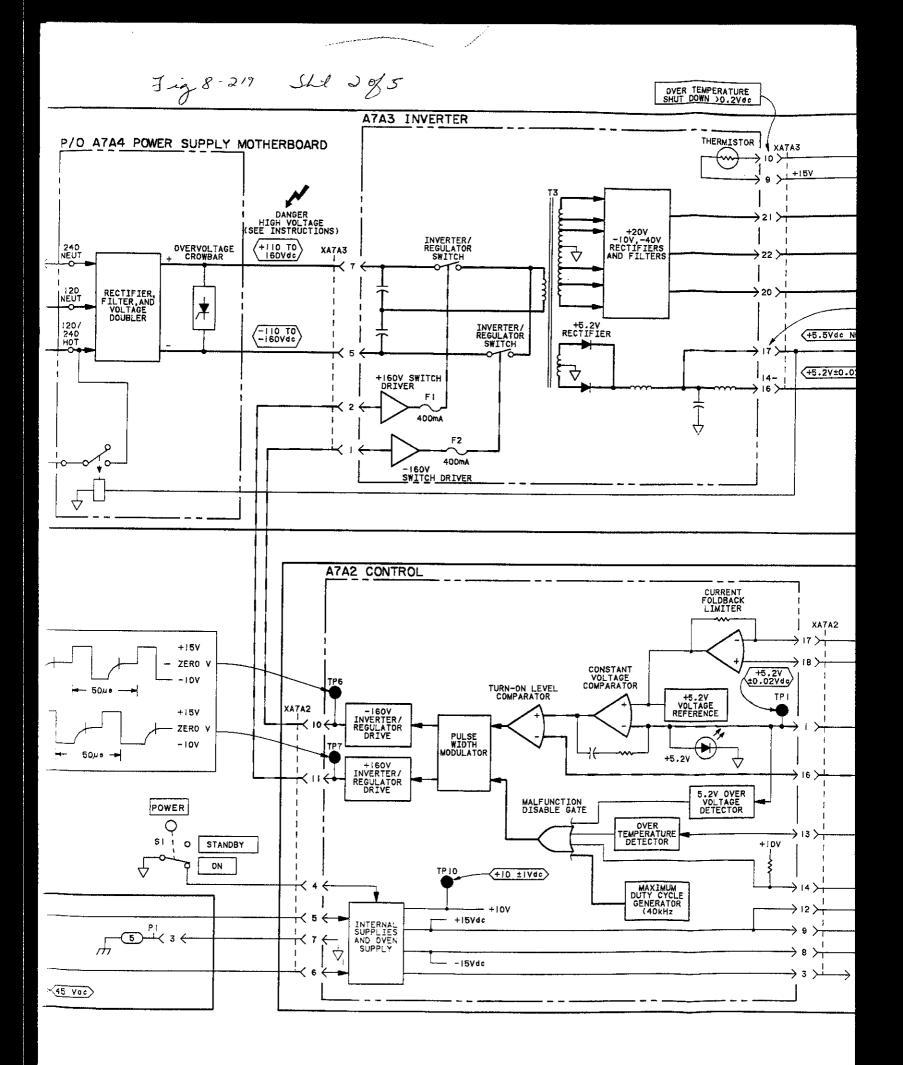

#### Power Supply

This instrument uses a switching-regulated power supply that provides high efficiency and low heat dissipation.

#### TROUBLESHOOTING

Introduction Troubleshooting is structured into three levels:

- 1. Instrument (to identify a defective section)

- 2. Section (to identify a defective assembly)

- 3. Assembly (to identify a defective component)

The general procedure is to begin at the instrument level to isolate the problem to a section (Block Diagram BD1), then to an assembly within the section (Block Diagrams BD2-BD10), and finally to a component on the assembly (detailed schematics). There is troubleshooting information on the block diagrams which can be used by someone who understands the theory of operation to isolate the problem to the next lower level. There is a troubleshooting procedure with each block diagram. These procedures are the recommended troubleshooting approach for someone who is inexperienced with servicing the Generator. To effectively use these procedures you need a basic understanding of the principles of operation. Read the theory before using the procedure so the procedure becomes a guide. Many short cuts are possible as more experience is gained.

## WARNING

When working on the power supply, remember that high voltage is present at all times when the line cord is plugged in (that is, plus and minus 160 Vdc and line voltage). Unplug the line cord before doing anything to the power supply. The line switch has no effect on the high voltage.

When working near the rear panel, be careful to keep long hair from being drawn into the fan. This could cause personal injury.

CAUTION

DO NOT plug in or unplug any board assembly with the instrument line switch turned on. Always turn the line switch to STANDBY when removing or inserting a board. There are some components that could be damaged by transients generated this way.

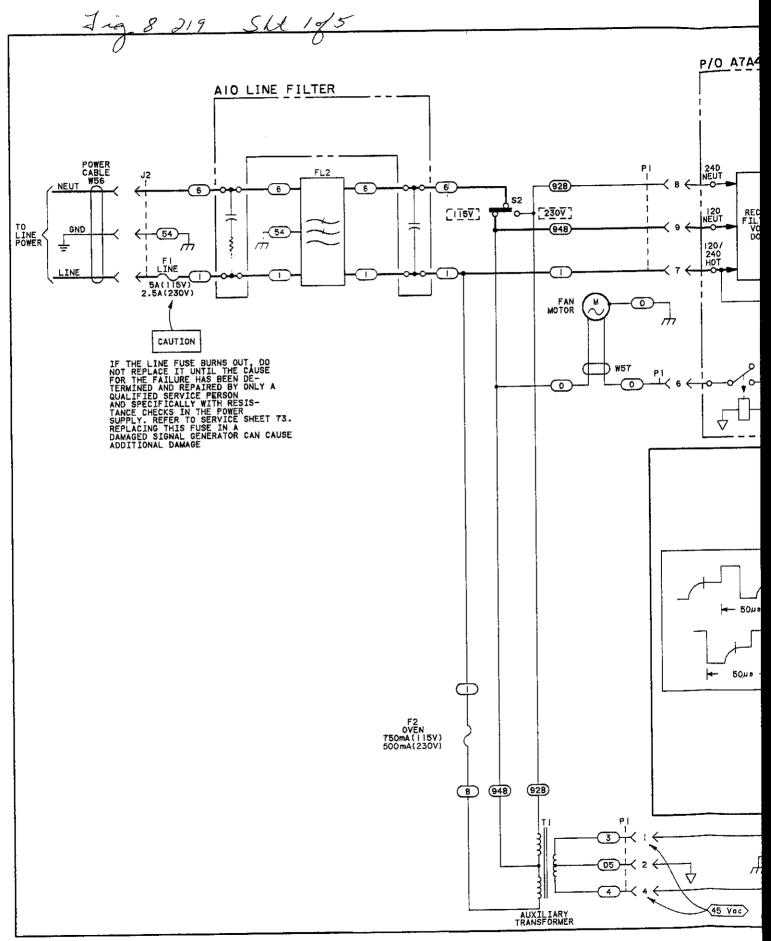

The "LINE" fuse should not be replaced until the cause of its failure is determined Replacing this fuse in a damaged Generator might cause additional damage. A qualified service person should first determine the cause of its failure, specifically with resistance checks in the power supply (see Service Sheet 65); repair the failure and then replace the fuse.

When measuring frequency, connect a cable from the Generator's 10 MHz Reference output (rear panel) to the counter's reference input and set the counter Reference switch to EXT. Since minor differences exist between time bases, using the 8663A's as a common reference will ensure that all correct frequency readings will be off only by the resolution error of the counter.

When measuring frequency or power level at an output connector, disconnect any cable that is normally connected so the measuring instrument is the only load on the output. If the cable must remain connected to make a valid measurement, this will be specifically stated.

All power level values given are as measured on a spectrum analyzer. Measurements made with a power meter might give a slightly higher reading. ECL signals will read approximately 2 dB higher with a

power meter because the harmonics are high and add to the power meter reading.

#### Instrument Level Troubleshooting Procedure

The followeing procedure can be used to isolate an instrument malfunction to one of the sections.

1. Check power supply voltages. Remove the top cover of the instrument. The power supply is in the left-rear corner. Test points used to check each of the voltages are accessible through openings in the power supply top cover. Silkscreening on the cover identifies the test points. Measure each of the voltages and compare to the tolerances in Table 8-201.

| Supply Voltage | Tolerance |

|----------------|-----------|

| +5.2V          | +.02V     |

| +20V           | +0.1V     |

| -10V           | +.04V     |

| -40V           | +0.2V     |

Table 8-201. Power Supply Voltages

If a voltage is out of tolerance, adjust it. The voltage should be adjustable above and below the nominal value within the tolerance limits. If a voltage cannot be adjusted to within limits, there is a problem with the power supply. Continue troubleshooting on Service Sheet BD10.

If the Generator fails to turn on, check the power supply voltages first. If they are incorrect, continue on Service Sheet BD10. If the power supply voltages are correct, continue on Service Sheet BD9 (the Digital Control Unit).

2. STATUS light flashes. All sections contain self-check circuitry which can detect some malfunctions. When a malfunction is detected, the STATUS light flashes. Press the STATUS key and hold it down and the status code will be displayed in the frequency display (on the right). If 99 is displayed, press the Blue Key and then the STATUS key. The actual status code will be displayed. Table 8-203 defines the malfunction status codes and where to continue troubleshooting if one occurs.

There are many errors which cannot be detected by the self-check circuitry and it's also possible for the self-check circuitry to

malfunction. Therefore, use the status code only as a guide. Confirm that the problem indicated by the status code really exists.

#### NOTE

Under certain conditions, it is possible for Status Code 76, "Amplitude out of specification", to turn on when no amplitude error exists. This can happen during fast repetitive sweeps (for example, Auto Sweep or Remote Stepped Sweep, with the time/step less than 1 ms). Corrective action is not required unless code 76 persists under conditions other than those outlined above.

If no status code is present, continue with Step 3.

- 3. All malfunctions can be divided into eight general classifications as follows:

- a) Front Panel, HP-IB and AUX malfunctions. This includes all improper operation of keys, display and indicators. Begin troubleshooting with Service Sheet BD9.

- b) RF output frequency not correct. Begin troubleshooting with Step 4.

- c) RF output power level not correct. Begin troubleshooting with Step 5.

- d) AM and FM problems. Begin troubleshooting with Service Sheet BD7.

- e) Phase modulation problems. Begin troubleshooting with Service Sheet BD8.

- f) Pulse modulation and BPSK problems. Begin troubleshooting with Service Sheet BD6.

- g) High spurs or phase noise. Begin troubleshooting with Step 6, below.

- h) Problems associated with front and rear panel connectors (except RF output). Table 8-202, shows where to start troubleshooting when the signal from an output connector is not normal or the signal applied to an input connector does not produce the desired effect.

| CONNECTOR                                                                                                                                                         | TROUBLESHOOT<br>ASSEMBLY (SERVICE SHEET)                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| AM IN, FM IN,<br>PM IN                                                                                                                                            | A11A5 (41 and 42)<br>A11A3 (44)                                                                                                                      |

| Rear Panel Connectors<br>AUX<br>SWP<br>AM MKR<br>Z/AXIS BLK/MKR<br>PLS BPSK<br>VMO OUT<br>AUX FM IM<br>(10 MHz Reference) OUTPUT<br>(5 or 10 MHz Reference) INPUT | A2A1 (61 and 62)<br>A2A2 (56 and 57)<br>A2A2 (56 and 57)<br>A2A2 (56 and 57)<br>A4A1 (37)<br>A11A1 (39 and 40)<br>A11A2 (43)<br>A8A4 (1)<br>A8A4 (1) |

#### Table 8-202. Failures Associated With External Connectors

- 4. RF Output Frequency Not Correct.

- a) Measure the RF output frequency with a counter. Run a cable from the Generator's 10 MHz reference output to the counter external time base input and set the counter time base switch to external.

- b) If the frequency is not stable (that is, it varies more than <u>+</u>1 count), there is a phase lock loop unlocked. Measure the output of each section containing phase lock loops shown on the block diagram until the bad section is found. Start at the bottom of the block diagram and move up. Then continue troubleshooting on the Service Sheet for the bad section.

- c) If the frequency is stable, measure the High Frequency Loops Section output frequency. If this frequency is normal, the problem is in the Output Section. Otherwise, measure the output of each section starting at the bottom of the block diagram until the bad section is found. Then continue troubleshooting on the service sheet for the bad section.

- 5. RF Power Level Not Correct. Measure the power level of the output signal from the High Frequency Loops Section. If this power level is not within the limits given on the block diagram, there is a problem in the High Frequency Loops Section so continue troubleshooting on Service Sheet BD3. If this power level is normal, the problem is in the Output Section, so continue troubleshooting on Service Sheet BD8.

#### Service

- 6. High Sprus or Phase Noise. This is the most difficult type of problem to troubleshoot. Some troubleshooting experience and a thorough understanding of the theory of operation of the instrument are needed to be successful. The general procedure to follow is:

- a) Locate the section of the instrument in which the problem is originating.

- b) Search for the cause. In the case of high phase noise it is now a matter of trying different approaches to narrow the range of possible causes. This is where experience helps. If the problem is spurs, identify the source of the spur. The location of the spur and how it moves in relation to the center frequency can provide a lot of information when the theory of operation of the Generator is understood. Removing cables or substituting signals from an external source are also useful techniques.

- c) Once the source of the spur is known look for the coupling mechanism.

| STA1<br>COL |                                                                                                                                               | CONTINUE<br>TROUBLESHOOTING<br>ON SERVICE SHEET |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| 00          | No malfunction                                                                                                                                |                                                 |

| 01          | Low reference oscillator signal level.                                                                                                        | 1                                               |

| 02          | (Check INT-EXT switches on rear panel).<br>Fractional-N Loop out on lock.                                                                     | BD4                                             |

| 03          | Low Frequency N Loop out of lock.                                                                                                             | BD4<br>BD5                                      |

| ŏ4          | Low Frequency Sum Loop out of lock.                                                                                                           | BD5                                             |

| 05          | Low Frequency FM Sum Loop out of lock.                                                                                                        | BD5                                             |

| 06          | High Frequency Reference Sum Loop out of lo                                                                                                   |                                                 |

| 07          | High Frequency Sum Loop out of lock.                                                                                                          | BD3                                             |

| 80          | FM Loop out of lock.                                                                                                                          | $BD\overline{7}$                                |

| 61          | Variable Modulation Oscillator Loop out of 1                                                                                                  | lock. BD7                                       |

| 76          | RF Output amplitude not leveled.                                                                                                              | BD8                                             |

| 95          | ROM Malfunction.                                                                                                                              | BD9                                             |

| 96          | RAM Malfunction.                                                                                                                              | BD9                                             |

| 98*         | Memory Malfunction.                                                                                                                           |                                                 |

| 99*         | Hardware Malfunction.                                                                                                                         |                                                 |

| t           | his is the general code for instrument malfun<br>he BLUE KEY and then STATUS to obtain one of<br>n the table which is the actual malfunction. | nction. Press<br>the other codes                |

TABLE 8-203. HARDWARE MALFUNCTION STATUS CODE DESCRIPTION

NOTE

Errors 101-119, below, are generated by self-check circuitry in the Digital Control Unit (DCU). The Frequency, level and modulation data that is sent to other sections is also read back from the DCU output. Thus, when an error occurs, it could be that the data is bad, something could be pulling the signal line up or down, or the read-back circuitry is bad. The description of the code gives the reference designator of the latch where the bad data is stored.

# TABLE 8-203. HARDWARE MALFUNCTION STATUS CODE DESCRIPTION (continued)

| STATUS<br>CODE | DESCRIPTION                   | CONTINUE<br>TROUBLESHOOTING<br>ON SERVICE SHEET |

|----------------|-------------------------------|-------------------------------------------------|

| 101 AM/F       | M Control (A2A4U15)           | 55                                              |

|                | ontrol (A2A4U16)              | 55                                              |

|                | Rate (A2A4U17)                | 55                                              |

|                | Rate (A2A4U14)                | 55                                              |

| 105 FM L       | evel (A2A4U13)                | 55                                              |

| 106 AM L       | EVEL (A2A4U12)                | 55                                              |

| 107 AM/F       | M Level (A2A4U11)             | 55                                              |

|                | evel (A2A10U13)               | 54                                              |

|                | evel (A2A10U14)               | 54                                              |

|                | ff Control (A2A10U15)         | 54<br>54                                        |

|                | evel (A2A10U12)               | 54                                              |

|                | evel (A2A10U11)               | 54                                              |

| 113 Not        |                               |                                                 |

|                | uency Range Control (A2A5U24) | 52,53                                           |

|                | uency DFO-DF1 (A2A5U23)       | 52,53                                           |

|                | uency DF2-DF3 (A2A5U26)       | 52,53                                           |

|                | uency DF4-DF5 (A2A5U25)       | 52,53                                           |

|                | uency DF6-DF9 (A2A5U21,U22)   | 52,53                                           |

| 119 Freq       | uency DFB7-DFB8 (A2A5U19,U20) | 52,53                                           |

SERIAL PREFIX: 2234A

NOTES

- 1. INTERCONNECTIONS BETWEEN THE DCU AND THE OTHER SECTIONS ARE NOT SHOWN ON THIS BLOCK DIAGRAM. REFER TO THE APPROPRIATE SECTION BLOCK DIAGRAM (UD2-BDIO) OR SCHEMATIC FOR THIS INFORMATION

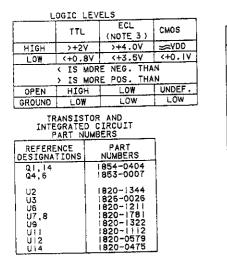

- 2. ECL LOGIC LEVELS IN THIS INSTRUMENT ARE NON-STANDARD DUE TO THE SUPPLY VOLTAGE USED. A HIGH LEVEL IS  $\geq$  +4.0V; A LOW LEVEL IS  $\leq$  +3.5V.

- 3. FREQUENCY FORMULAS GIVEN FOR BLOCK DIAGRAMS BD3. BD4 AND BD5, APPLY ONLY WHEN THE FRONT PANEL FREQUENCY SETTING IS BETWEEN 320 AND 640 MHZ (THAT IS. THE BASIC 8AND). THE FORMULAS DO NOT APPLY IF A FREQUENCY FAILURE OCCURS OUTSIDE THE BASIC BAND. FREQUENCY FAILURES OUTSIDE THE BASIC BAND ARE PROBABLY IN THE OUTPUT SECTION (REFER TO BD6 TO BEGIN TROUBLESHOOTING).

THE FORMULAS RELATE TO THE FRONT PANEL FREQUENCY DISPLAY. THE DISPLAY DIGITS ARE DESIGNATED  ${\rm D}_{10}$  through  ${\rm D}_0$  as follows:

FREQUENCY DISPLAY  $D_{10} D_9 D_8 D_7 D_6 D_5 D_4 D_3 D_2 D_1 D_0$

ENTER THE VALUE OF EACH DIGIT INTO THE FORMULAS AND USE THE DECIMAL POINT SHOWN IN THE FORMULA INSTEAD OF THE DISPLAYED DECIMAL POINT.

.: 19 FOR EXAMPLE IF THE DISPLAYED FREQUENCY IS 532.876 401 9 MHz

- THE OUTPUT OF BD3 WOULD BE: 532.876 401 9 MHz

- THE OUTPUT OF 804 WOULD 8E: 200-76.401 9 MHz OR 123.5981 MHz

- THE OUTPUT OF 805 WOULD BE: 10 + 2.876 40! 9 MHz OR 12.876 40! 9 MHZ

IF THE LINE FUSE BURNS OUT DO, NOT REPLACE IT UNTIL THE CAUSE OF THE FAILURE HAS BEEN DETER-MINED AND REPAIRED BY A QUALIFIED SERVICE PERSON AND, SPECIFICALLY, WITH RESISTANCE CHECKS IN THE POWER SUPPLY. REFER TO SERVICE SHEET 65. REPLACING THIS FUSE IN A DAMAGED SIGNAL GENERATOR CAN RESULT IN ADDITIONAL DAMAGE

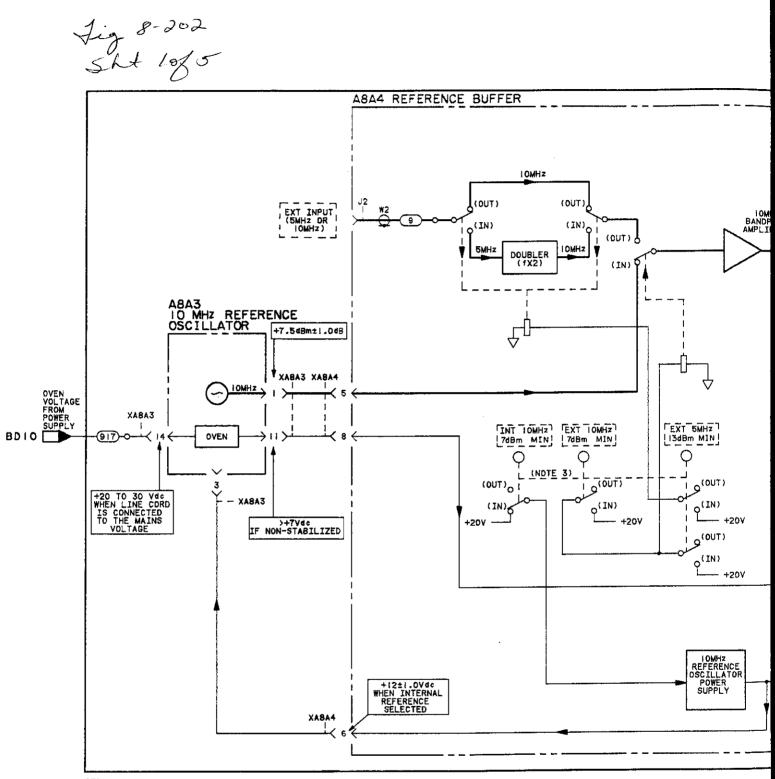

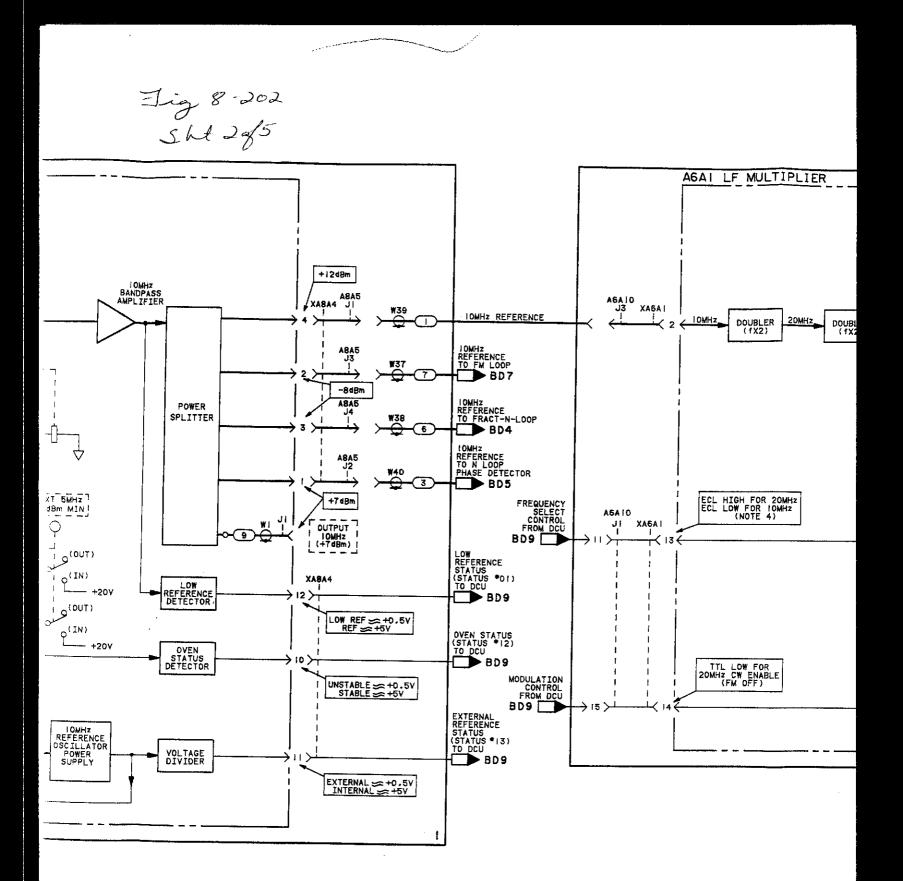

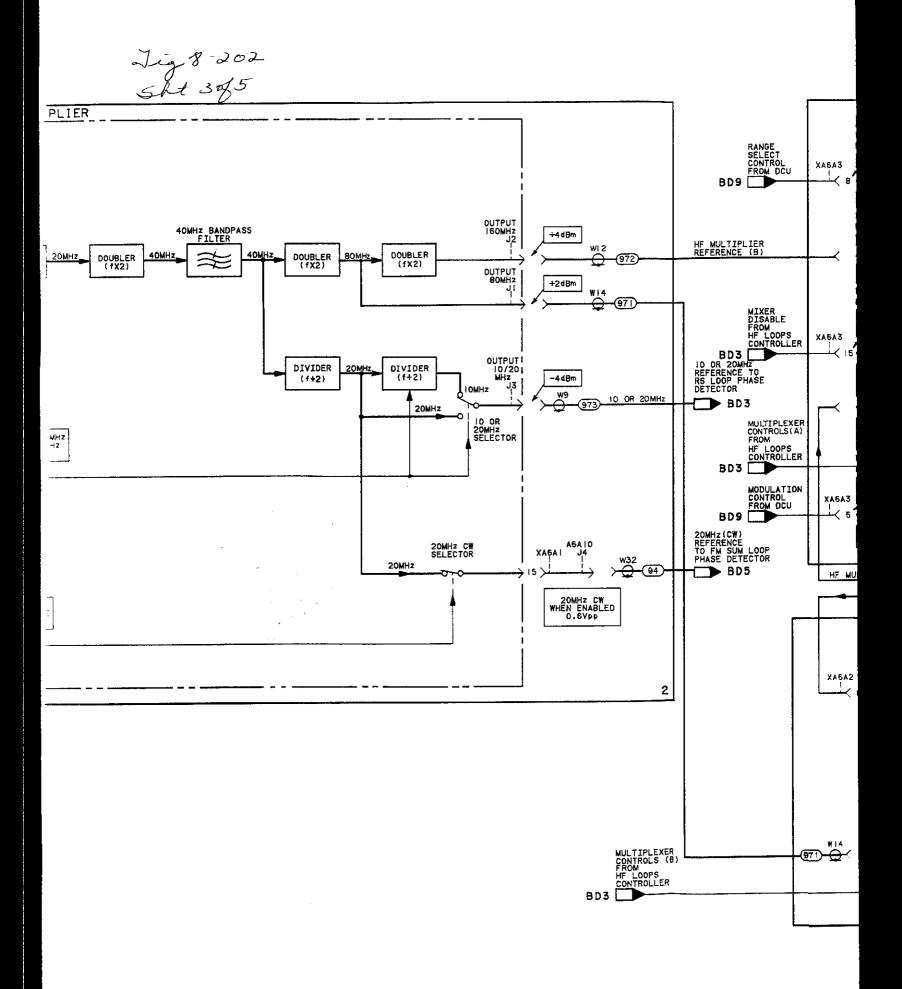

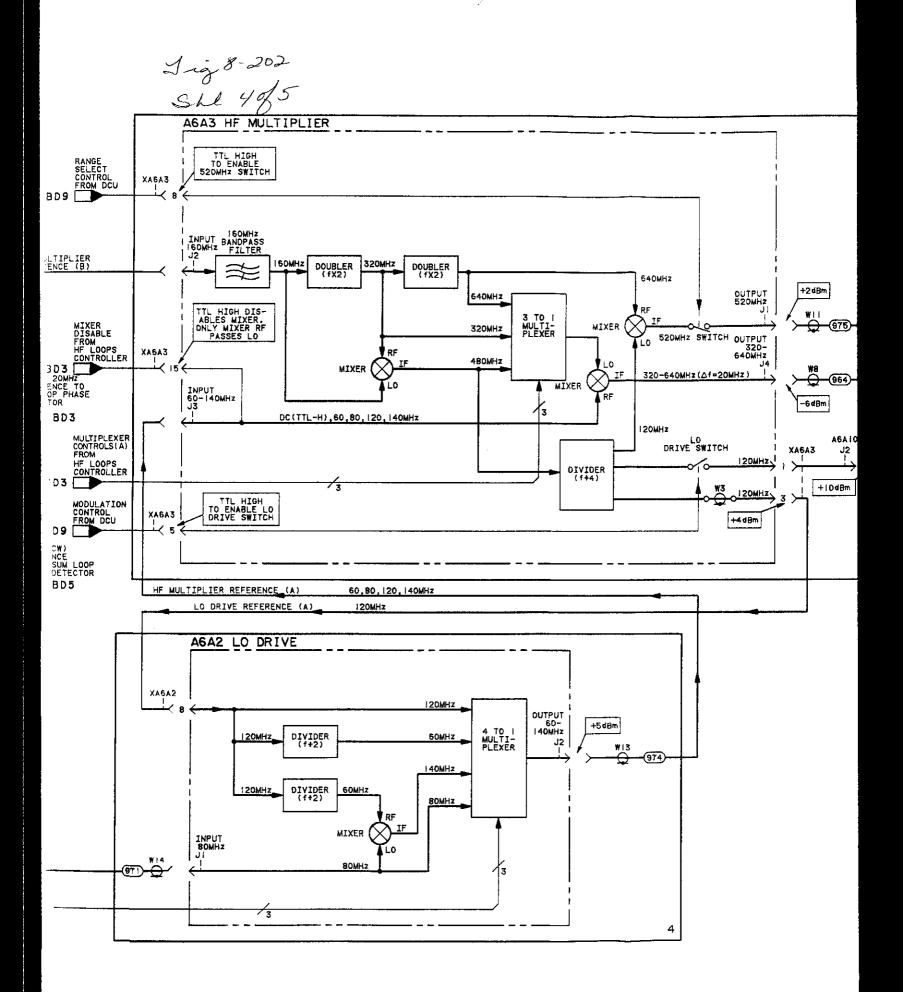

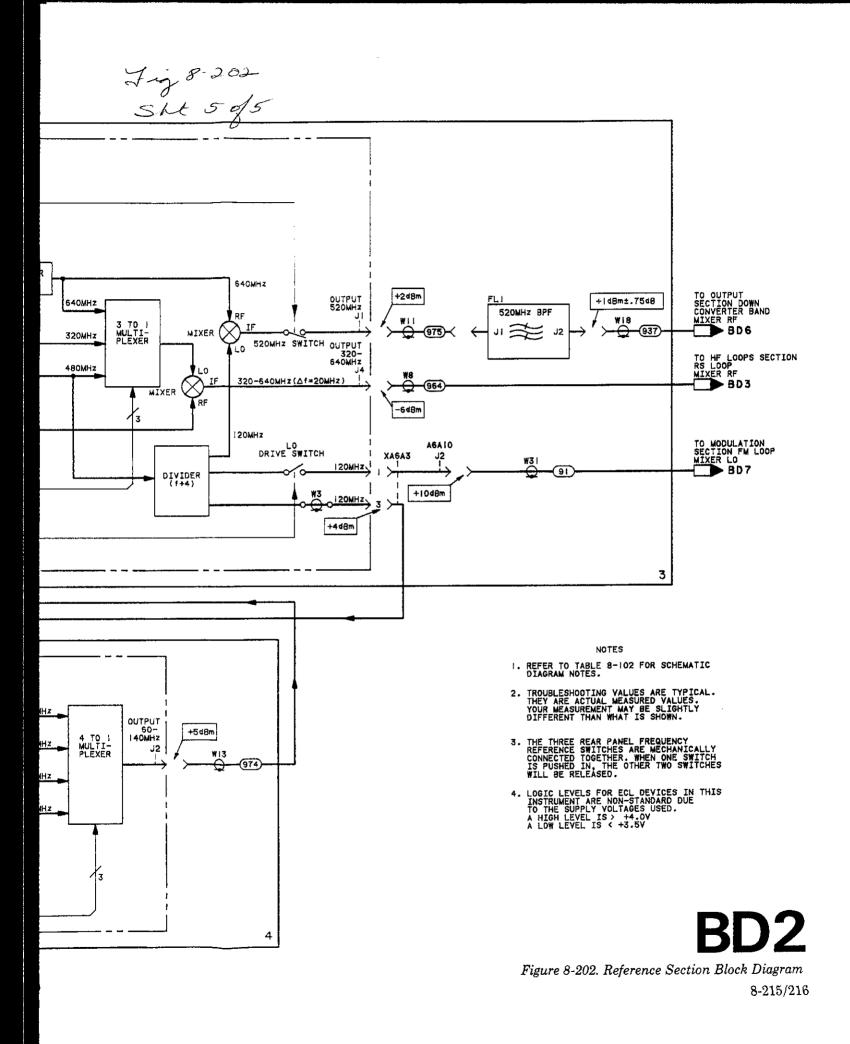

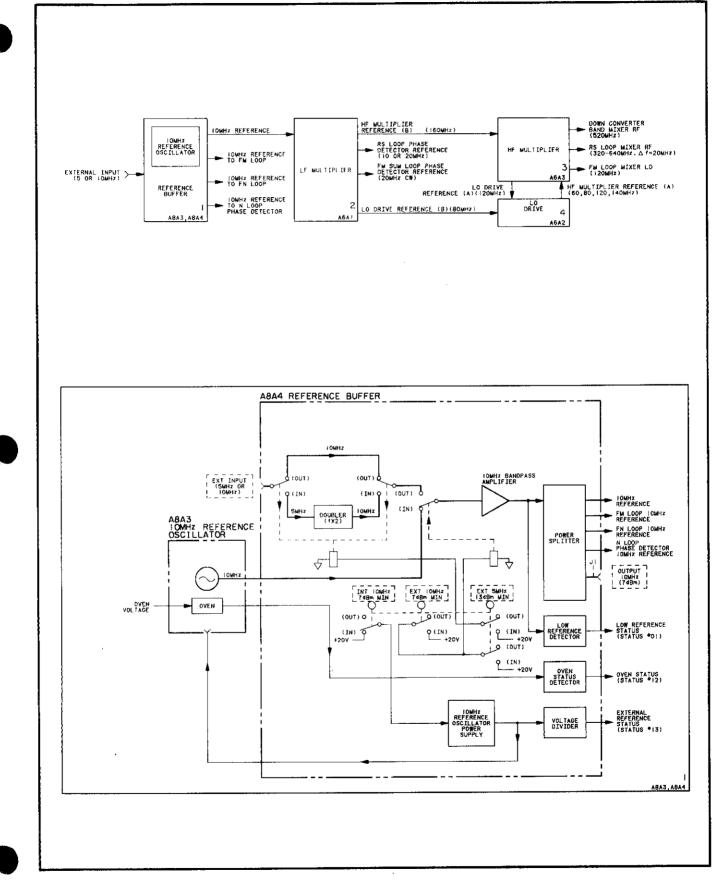

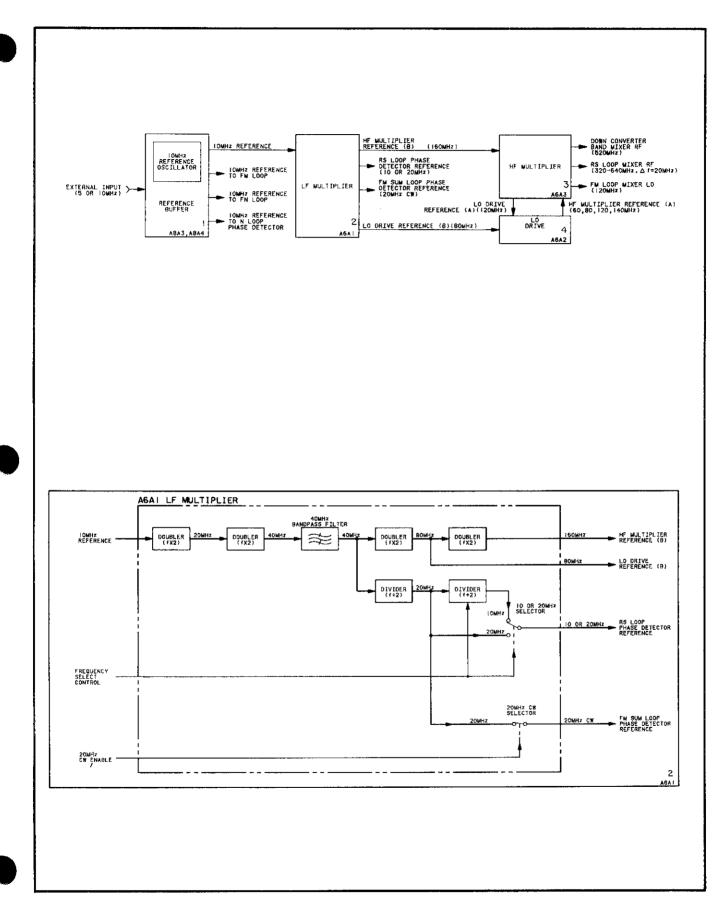

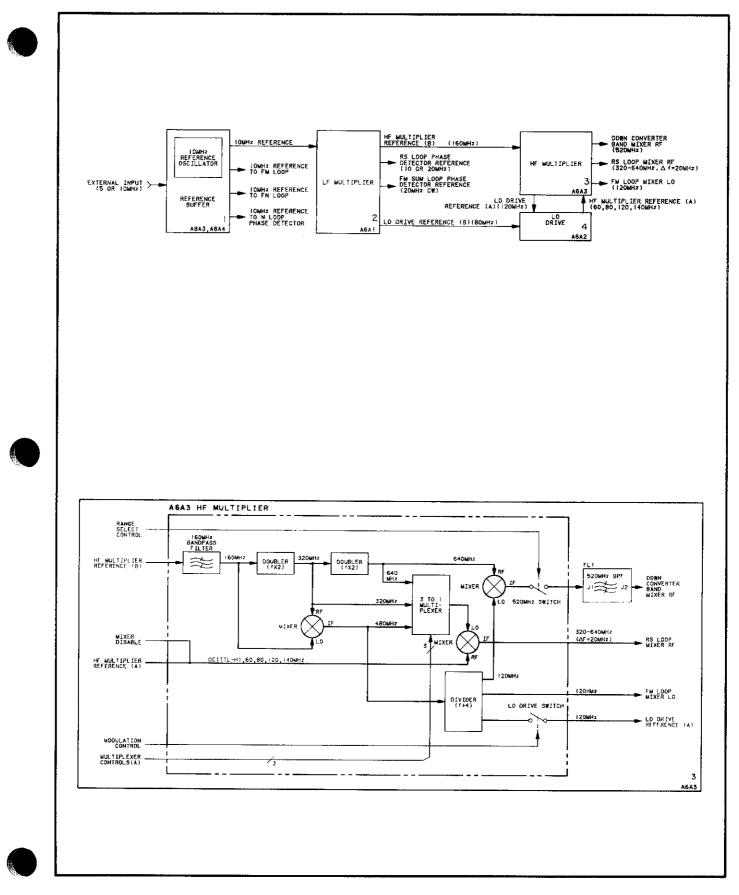

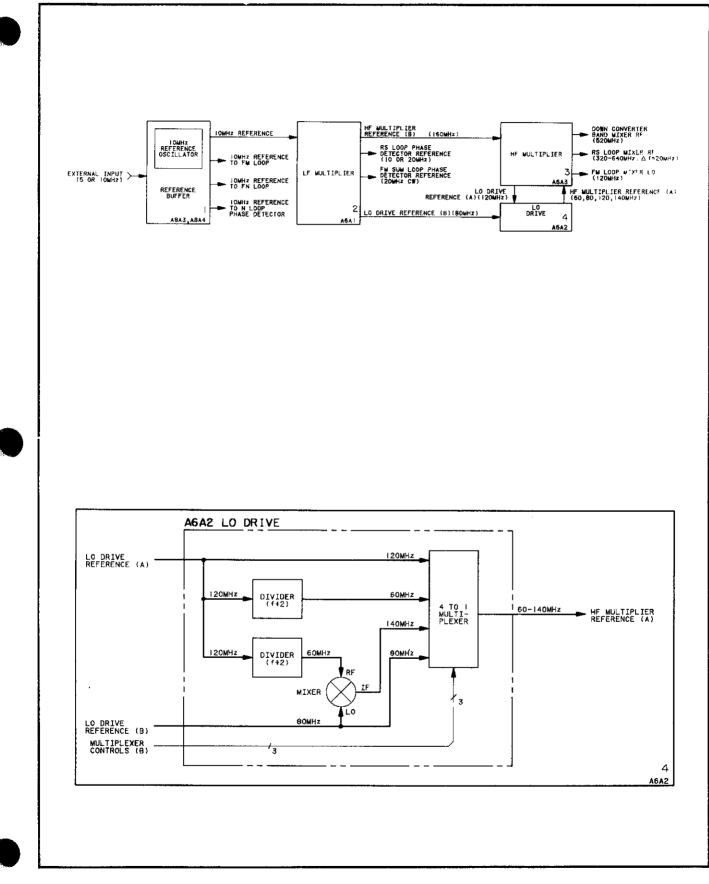

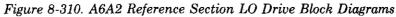

SERVICE SHEET BD2 REFERENCE SECTION BLOCK DIAGRAM

REFERENCE BD1 Simplified Operation (Section III) Operator's Checks (Section III) Table 4-1. Recommended Performance Tests After Adjustments or Repairs. Table 5-2. Post-Repair Adjustment Procedures.

#### PRINCIPLES OF OPERATION

The Reference Section provides the following output signals:

FM Loop 10 MHz Reference Signal Fract. N 10 MHz Reference Signal N Loop Phase Detector Reference (10 MHz) RS Loop Phase Detector Reference (10 or 20 MHz) FMS Loop Phase Detector Reference (20 MHz CW) Down Converter Band Mixer RF (520 MHz) RS Loop Mixer RF (320-640 MHz, delta f = 20 MHz) FM Loop Mixer LO (120 MHz)

These signals are distributed to other sections of the instrument. All of the Reference Section outputs are derived from either a 10 MHz internal source (temperature controlled quartz oscillator) or an external frequency standard of 5 MHz or 10 Mhz. The accuracy and stability of all signals generated in the Generator are traceable to the outputs from the Reference Section. The various output signals are generated by employing several frequency translation techniques (multiplying, dividing and heterodyning).

#### TROUBLESHOOTING

There are five signals generated in the Reference Section ( besides three 10 MHz signals) and sent to other sections of the instrument:

- 1) 320-640 MHz in 20 MHz steps (A6A3J4)

- 2) 520 MHz reference signal (A6A3J1

- 3) 120 MHz reference signal (A6A10J2)

- 4) 10/20 MHz signal (A6A1J3)

- 5) 20 MHz reference signal when the instrument is in FM mode (A6A10J4)

When the frequency or level of one of these signals is not the value shown on the block diagram, the problem is in the Reference Section. Table 8-205 shows at what frequencies the variable frequency signals are for output frequencies in the basic band (that is, 320 to 640 MHz). Troubleshoot the Reference Section by backtracking until the bad assembly is found. Then continue troubleshooting with the service sheet for the defective assembly.

| Outp<br>Frequenc |       |           | Section Variable | -                   |

|------------------|-------|-----------|------------------|---------------------|

|                  |       | A6A3J4    | A6A1J3           | A6A2J2 <sup>1</sup> |

| <u>&gt;</u>      | <     | (320-640) | (10/20)          | (60-140)            |

| 320.0            | 330.0 | 320.0     | 10.0             | DC                  |

| 330.0            | 340.0 | 340.0     | 20.0             | 140.0               |

| 340.0            | 350.0 | 340.0     | 10.0             | 140.0               |

| 350.0            | 360.0 | 360.0     | 20.0             | 120.0               |

| 360.0            | 370.0 | 360.0     | 10.0             | 120.0               |

| 370.0            | 380.0 | 380.0     | 20.0             | 60.0                |

| 380.0            | 390.0 | 380.0     | 10.0             | 60.0                |

| 390.0            | 400.0 | 400.0     | 20.0             | 80.0                |

| 400.0            | 410.0 | 400.0     | 10.0             | 80.0                |

| 410.0            | 420.0 | 420.0     | 20.0             | 60.0                |

| 420.0            | 430.0 | 420.0     | 10.0             | 60.0                |

| 430.0            | 440.0 | 440.0     | 20.0             | 120.0               |

| 440.0            | 450.0 | 440.0     | 10.0             | 120.0               |

| 450.0            | 460.0 | 460.0     | 20.0             | 140.0               |

| 460.0            | 470.0 | 460.0     | 10.0             | 140.0               |

| 470.0            | 480.0 | 480.0     | 20.0             | DC                  |

| 480.0            | 490.0 | 480.0     | 10.0             | DC                  |

| 490.0            | 500.0 | 500.0     | 20.0             | 140.0               |

| 500.0            | 510.0 | 500.0     | 10.0             | 140.0               |

| 510.0            | 520.0 | 520.0     | 20.0             | 120.0               |

| 520.0            | 530.0 | 520.0     | 10.0             | 120.0               |

| 530.0            | 540.0 | 540.0     | 20.0             | 60.0                |

| 540.0            | 550.0 | 540.0     | 10.0             | 60.0                |

| 550.0            | 560.0 | 560.0     | 20.0             | 80.0                |

| 560.0            | 570.0 | 560.0     | 10.0             | 80.0                |

| 570.0            | 580.0 | 580.0     | 20.0             | 60.0                |

| 580.0            | 590.0 | 580.0     | 10.0             | 60.0                |

| 590.0            | 600.0 | 600.0     | 20.0             | 120.0               |

| 600.0            | 610.0 | 600.0     | 10.0             | 120.0               |

| 610.0            | 620.0 | 620.0     | 20.0             | 140.0               |

| 620.0            | 630.0 | 620.0     | 10.0             | 140.0               |

| 630.0            | 640.0 | 640.0     | 20.0             | DC                  |

Table 8-205. Reference Section Variable Frequency Signals

1

SERIAL PREFIX: 2234A

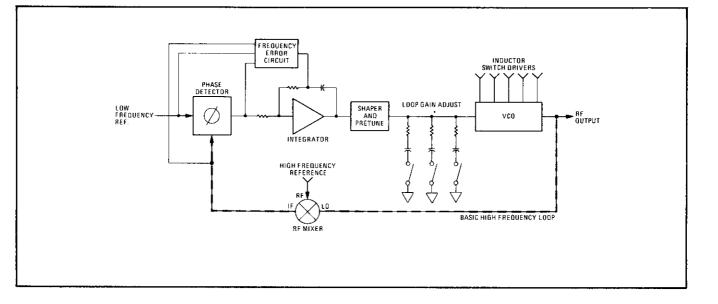

SERVICE SHEET BD3 HIGH FREQUENCY LOOPS BLOCK DIAGRAM

REFERENCE BD1

Simplified Operation (Section III) Operator's Checks (Section III) Table 4-1. Recommended Performance Tests After Adjustments or Repairs. Table 5-2. Post-Repair Adjustment Procedures.

#### PRINCIPLES OF OPERATION

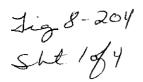

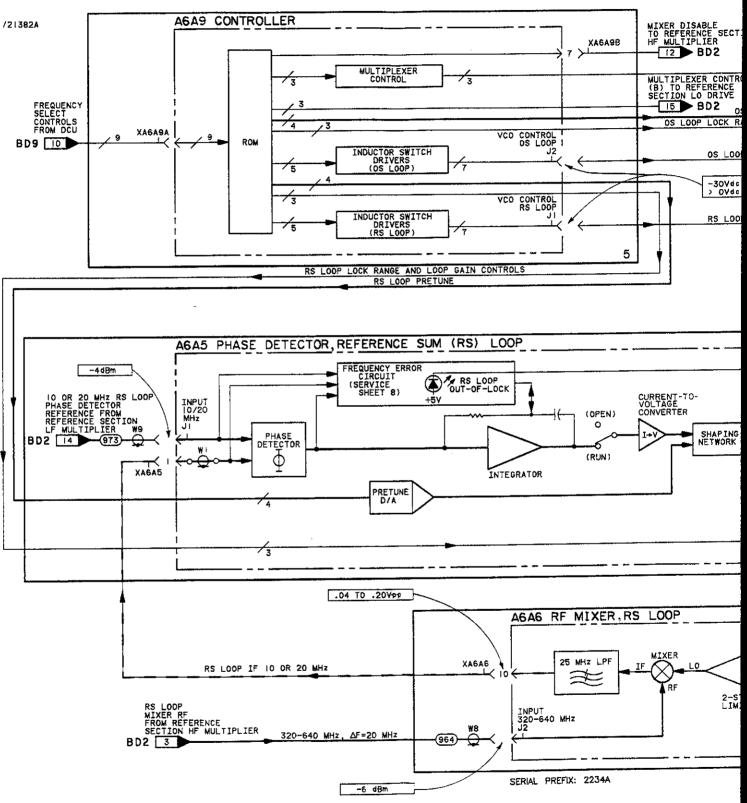

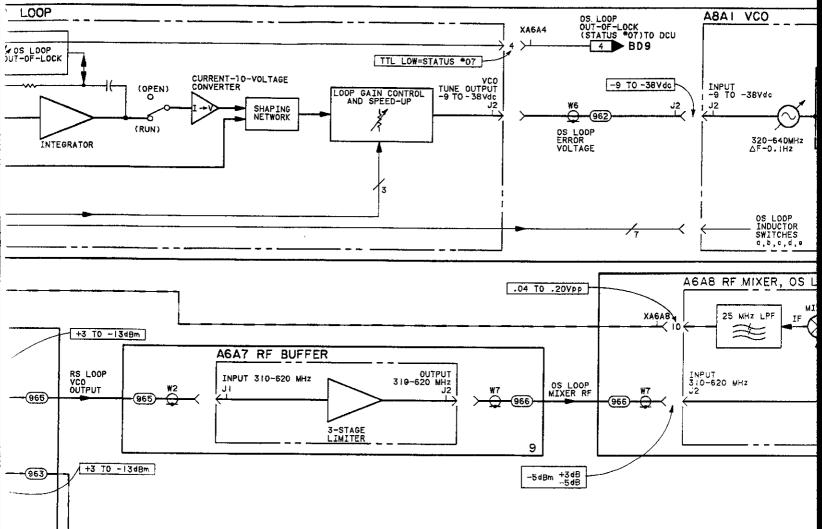

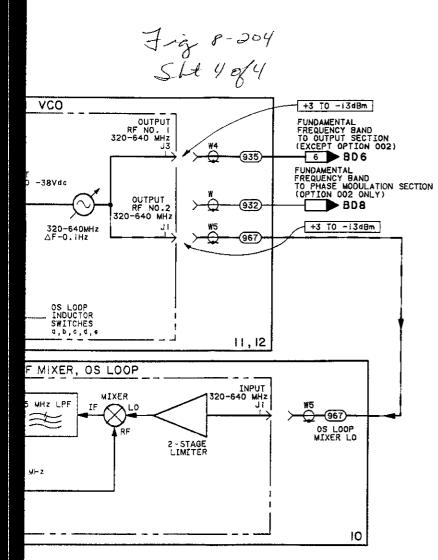

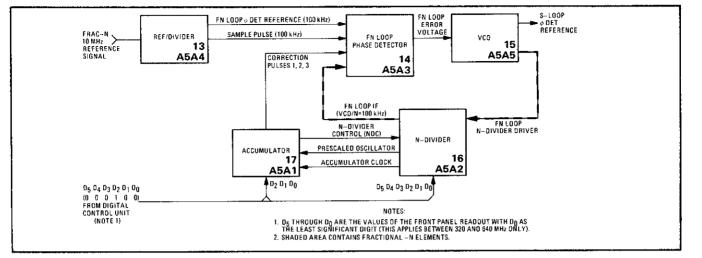

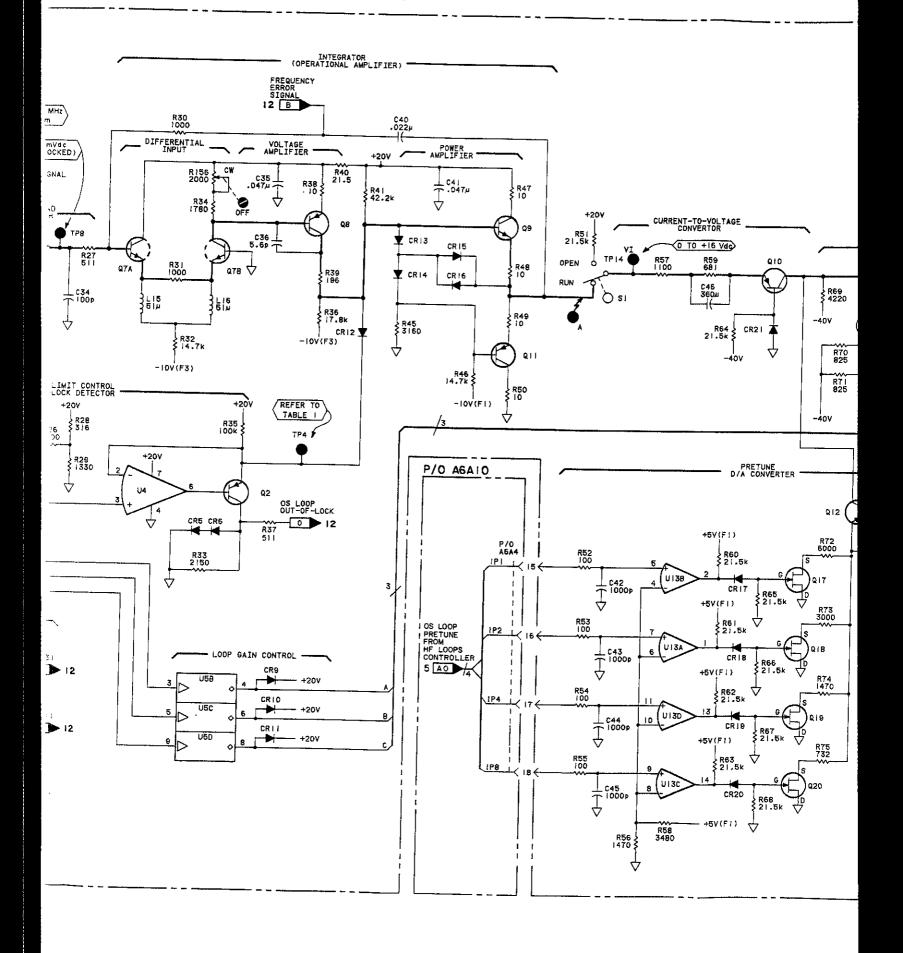

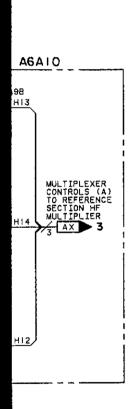

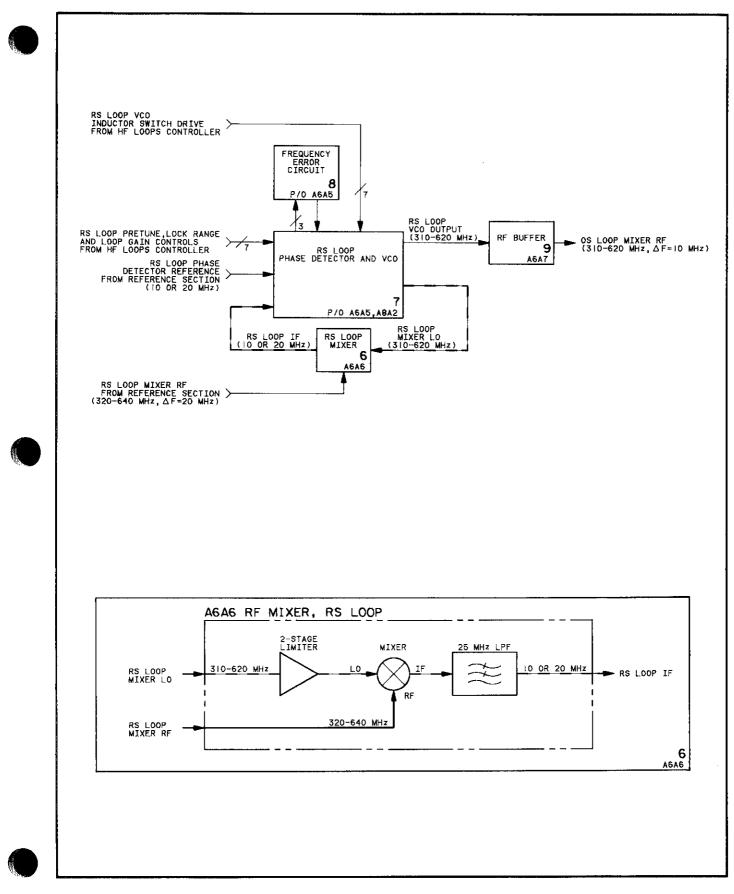

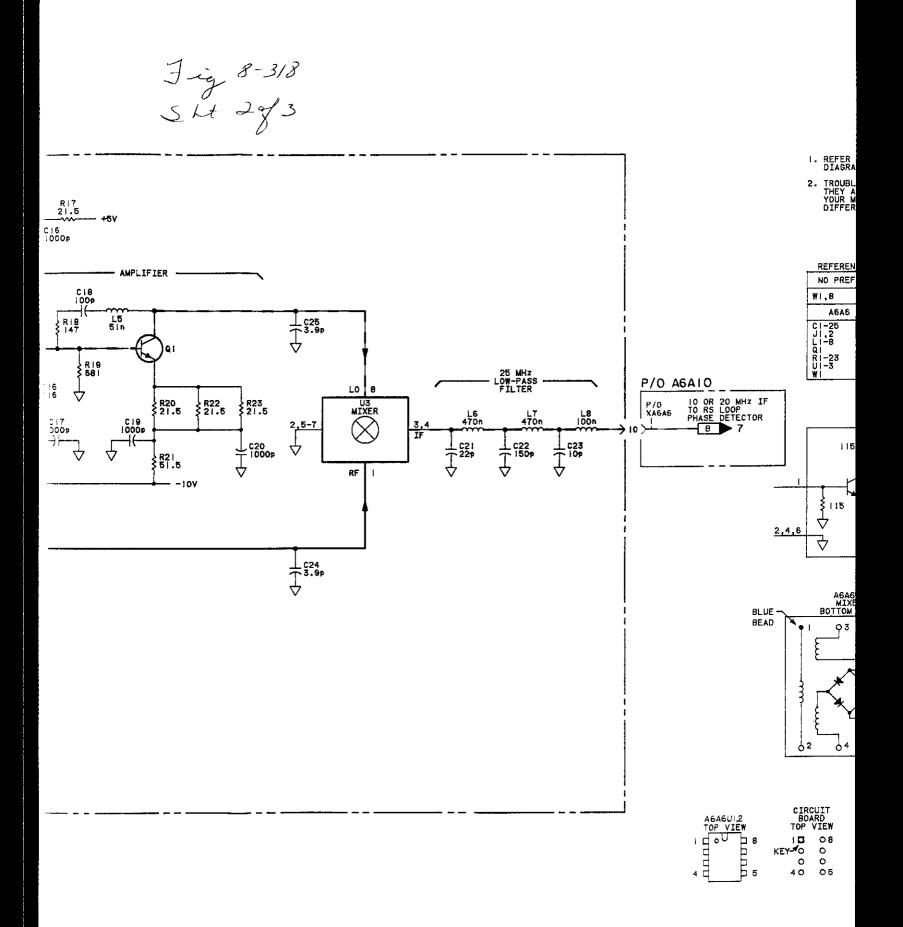

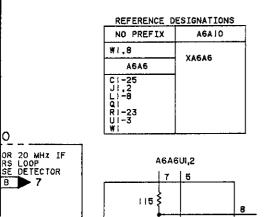

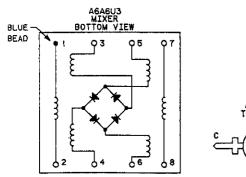

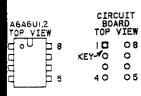

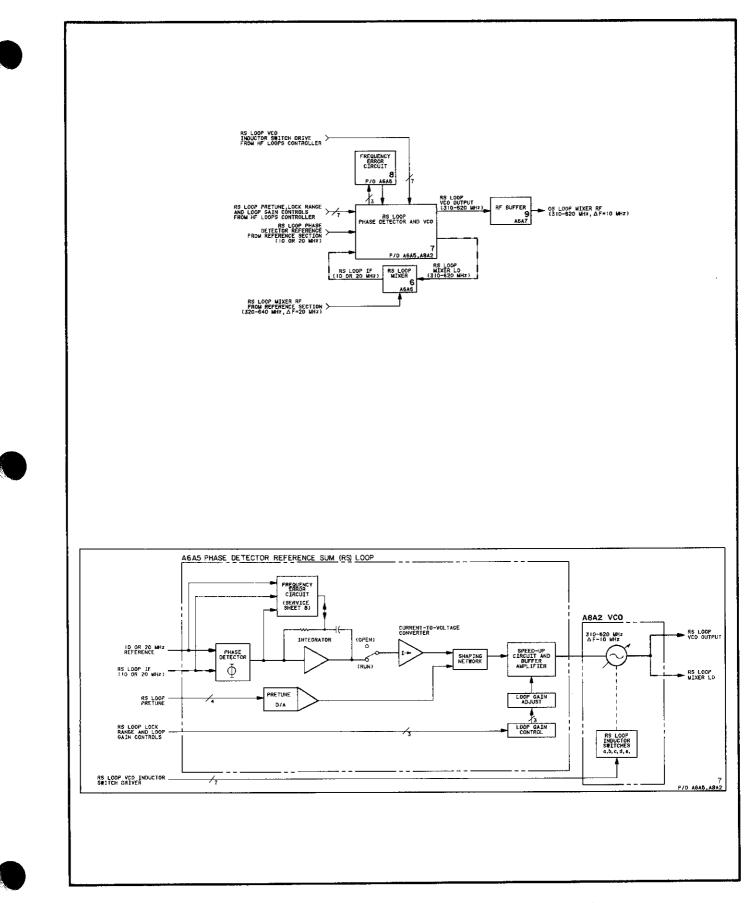

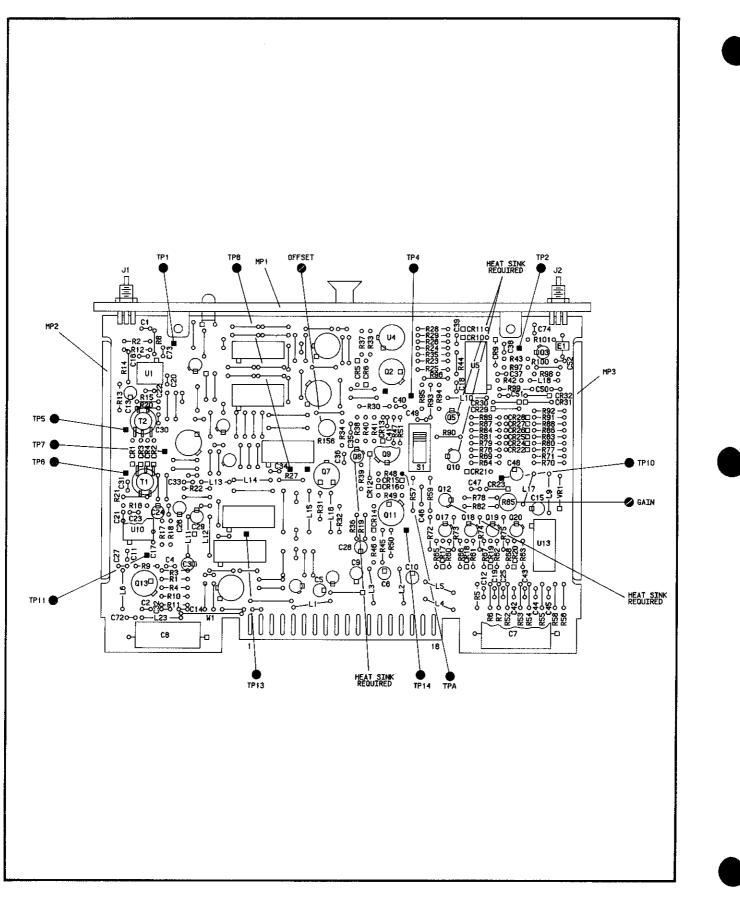

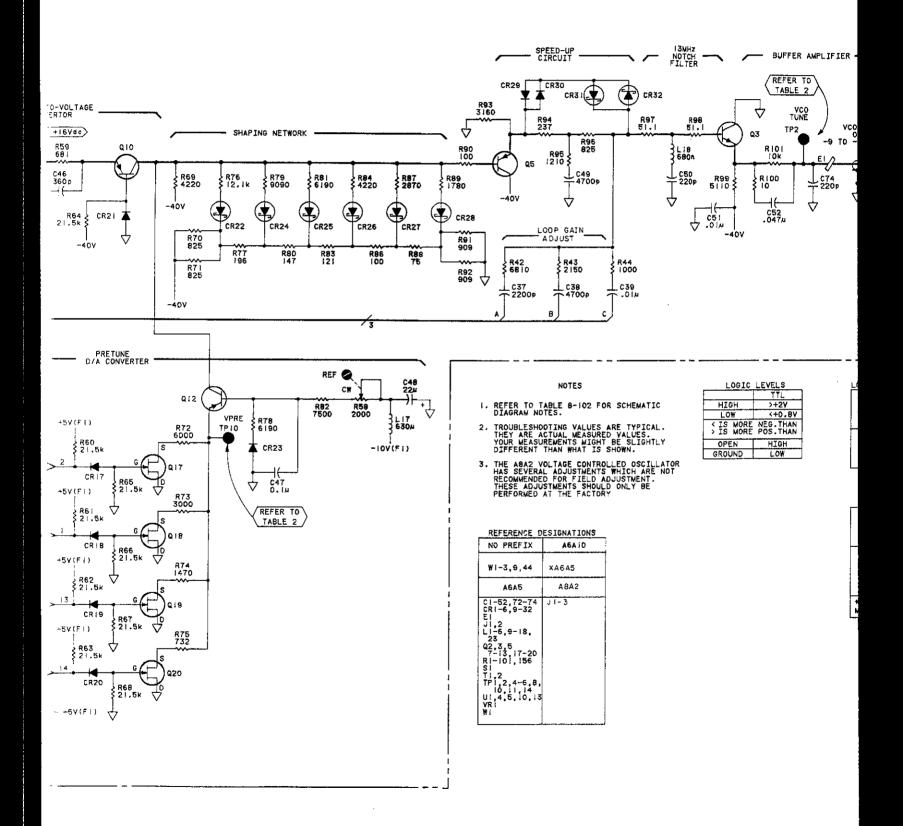

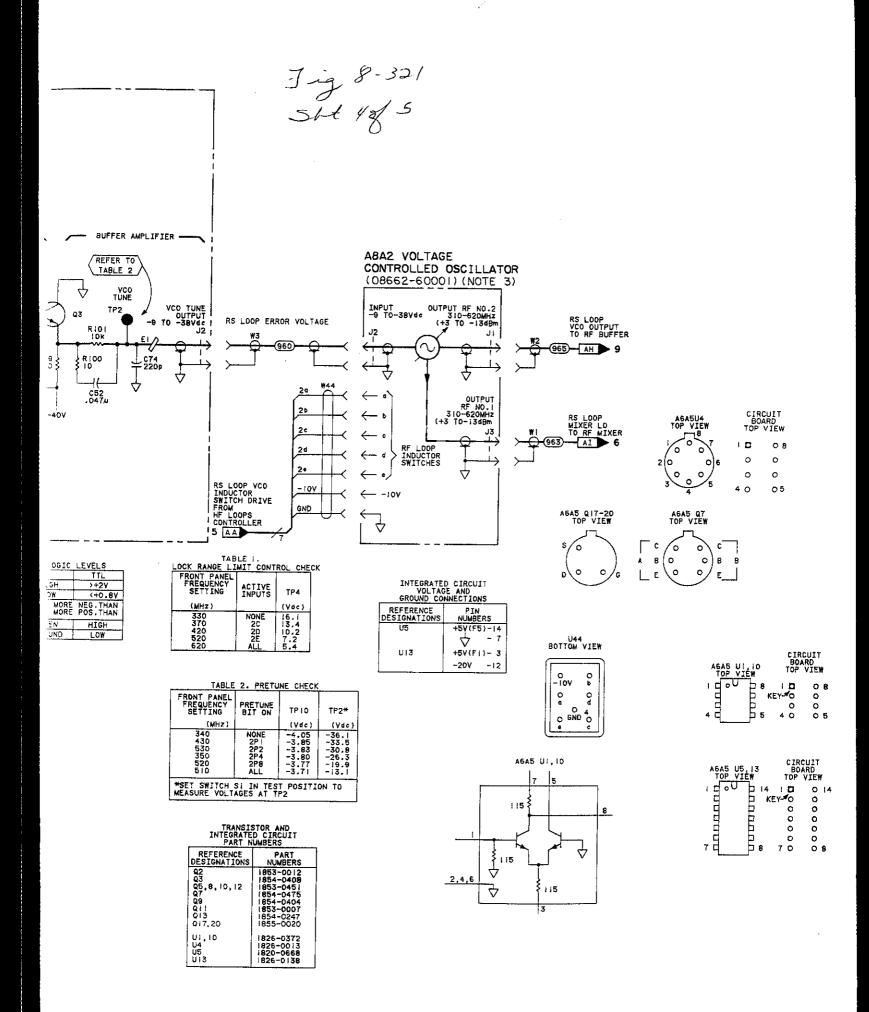

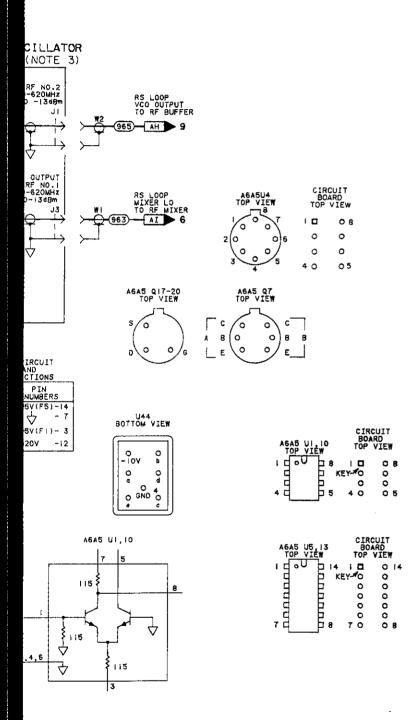

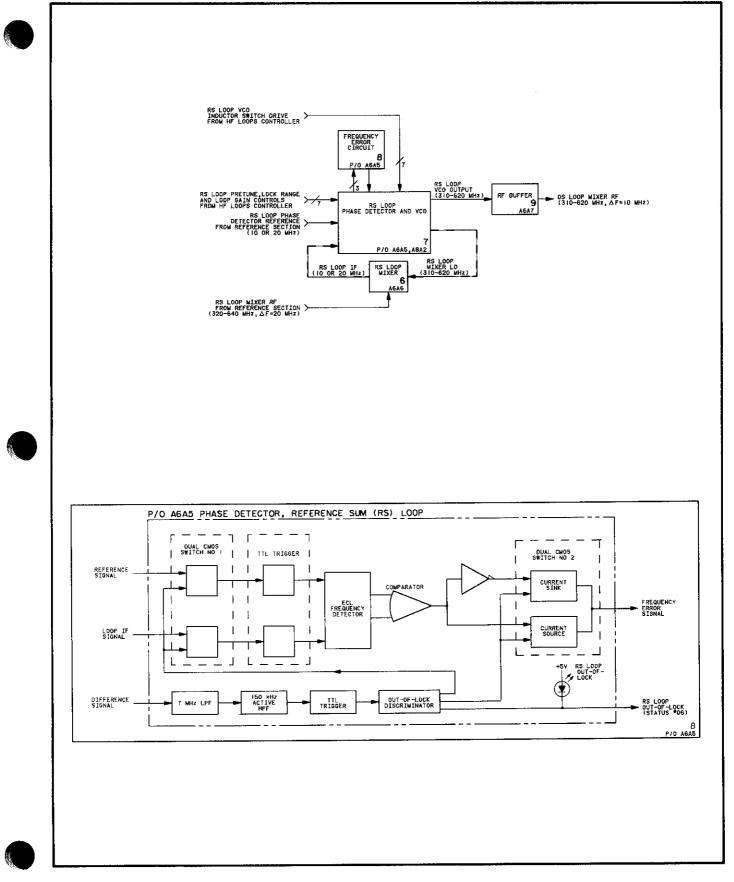

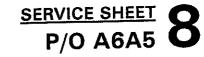

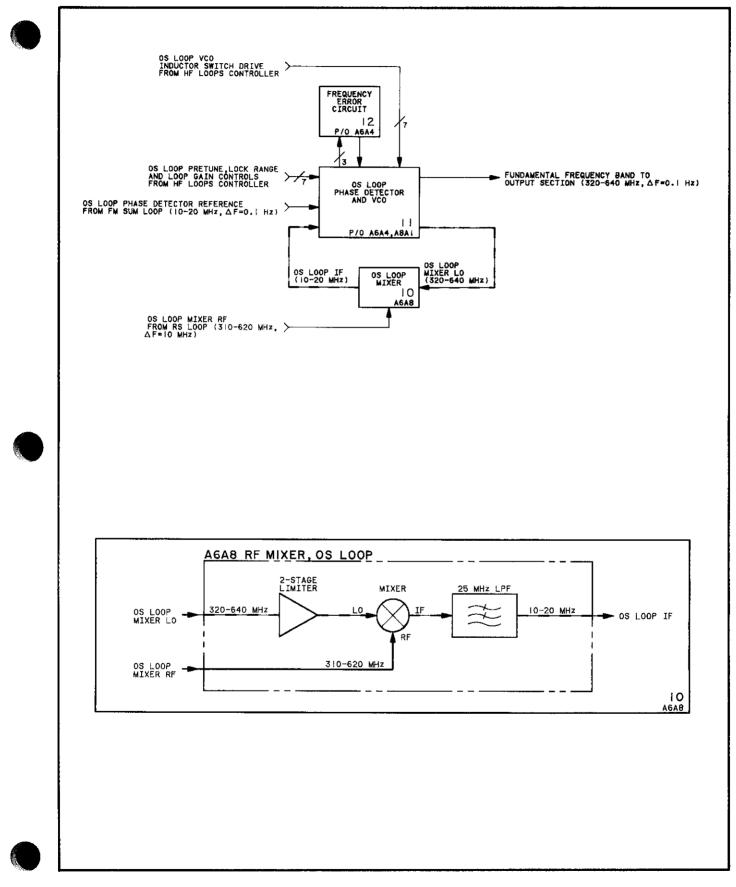

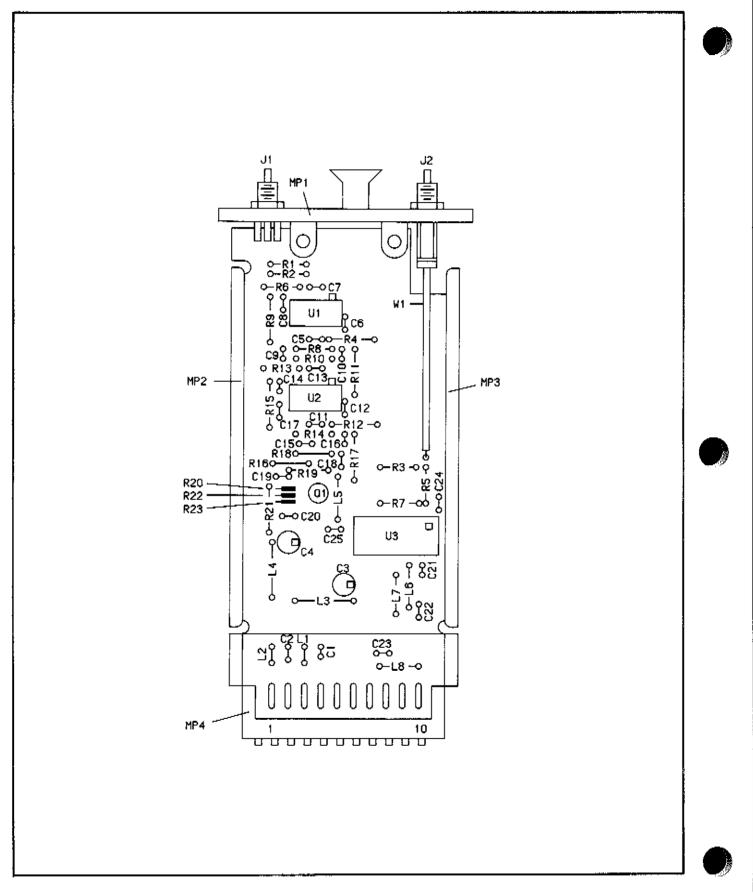

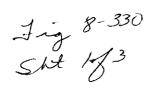

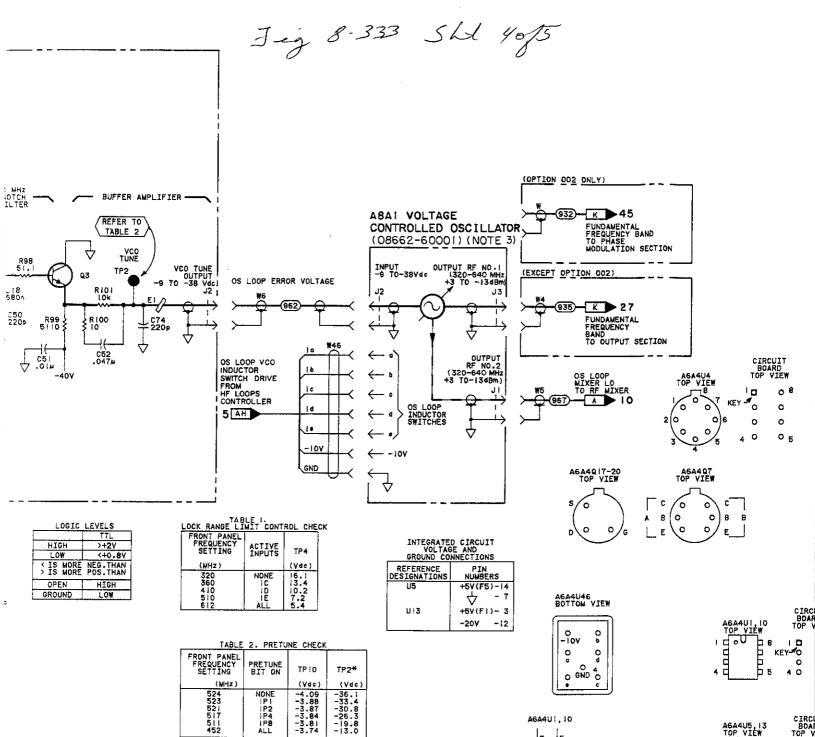

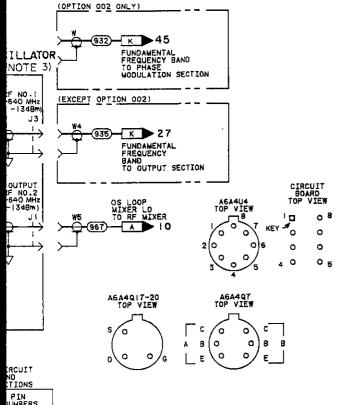

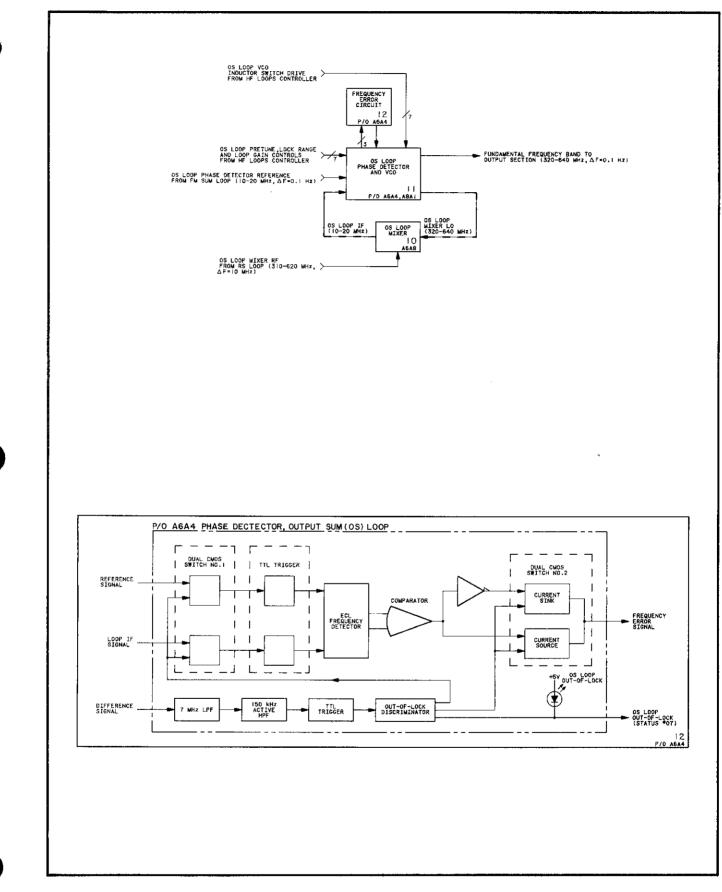

The High Frequency Section generates the basic (fundamental) band which is sent to the Output section (Service Sheet BD6). This section employs two phase lock loops to generate the basic band. The 320 to 640 MHz and 10/20 MHz signals from the Reference Section are first mixed in the Reference Sum Loop to produce a 310 to 620 MHz, 10 MHz step resolution signal. This signal is then mixed in the Output Sum Loop with the 10 or 20 MHz. 0.1 Hz step resolution, signal from the Low Frequency Loops Section to produce the 320 MHz to 640 MHz , 0.1 Hz step resolution, basic band signal at the A8A1J3 output. Figure 8-203 is a block diagram of the basic high frequency loop. The only difference between the Reference Sum (RS) Loop and the Output Sum (OS) Loop is that, in the case of the RS Loop, the VCO output frequency is always less than the high frequency reference input at the mixer, whereas the opposite is true for the OS Loop. Coarse tuning and speedup is regulated by the Controller Board (Service Sheet 5) in the High Frequency Loops Section.

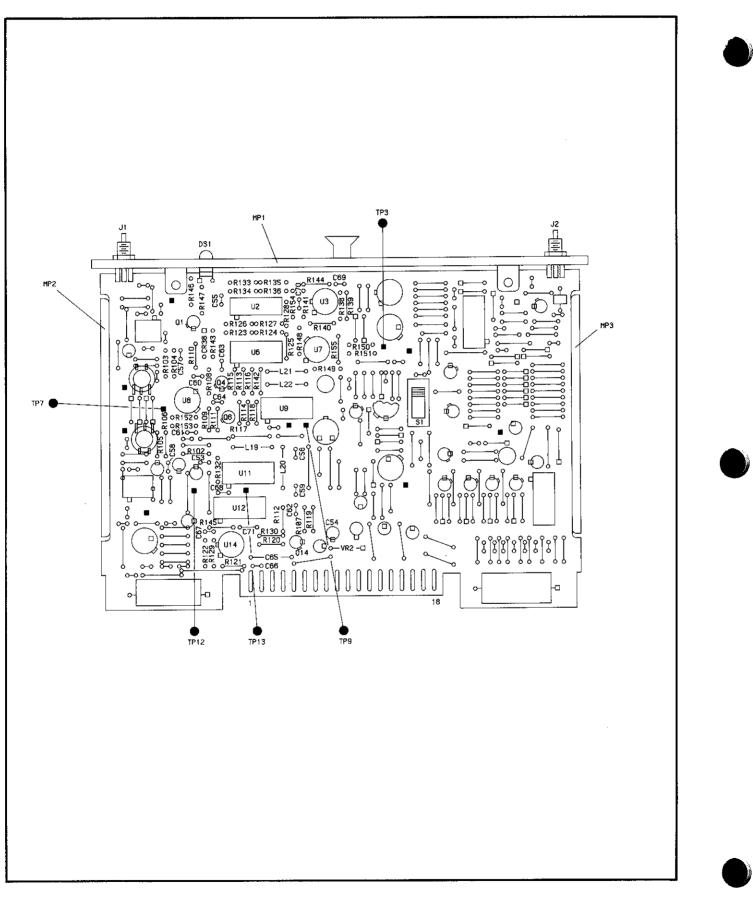

The frequency error circuits (Service Sheets 8 and 12) contain the frequency comparator and VCO correction circuitry. Under normal operating conditions, when the VCOs are locked, these lock acquisition circuits remain inactive. When the loop is un-locked, a beat note exists which is the difference between the loop IF down converted frequency and the reference frequency. If this beat note is within 200 kHz of the loop bandwidth (which is between 250 kHz and 500 kHz) the loop will acquire lock by itself. If the beat note is greater than the loop bandwidth by more than 200 kHz, the lock acquisition circuitry will be activated, coarsely tuning the VCO to within 200 kHz of the desired frequency. At this point, the phase lock loop will take over and complete the lock cycle.

#### TROUBLESHOOTING

When a problem has been traced to the High Frequency Loop section, this procedure can be used to isolate the problem to an assembly. The Reference Sum (RS) Loop must be locked before the Output Sum (OS) Loop will lock, therefore, work on the RS Loop first if both are unlocked.

#### Procedure:

- 1. Set the front panel frequency to a value in the basic band (320.0 to 640.0 MHz). If the problem doesn't occur in this band, the fault is most likely in the Output Section (Service Sheet BD6) rather than the HF Loops Section.

- 2. Measure the input signals to the loop being tested. These input signals are described in Table 8-206. If any of the input signals are not normal, look for the problem at the source of the input signal.

- 3. Pull out the A6A4 (OS Loop) or A6A5 (RS Loop) assembly and move the slide switch to the TEST position. This opens the loop so the VCO can be checked. Use Table 8-207 or Table 8-208 depending on the loop being checked, and check the VCO output for the front panel frequency settings given in the table. If the VCO functions normally, continue troubleshooting with step 4. If the VCO output is not normal, check the two input signals to the VCO.

- a) The tuning voltage should be the value given in the table. If the voltage is not normal, there is most likely a problem in the pretuning circuitry on A6A4 or A6A5 (whichever drives the VCO where the problem exists).

- b) The inductor switch signals. The table states which inductor should be turned on. Sevice Sheet 5 shows the pin numbers where the switch signals can be measured and what the normal levels are. If the switch signals are not normal, the problem is most likely on A6A9.

If the input signals are normal and the VCO output is bad, then the VCO is defective. The VCOs are not field-repairable. Exchange assemblies are available.

| Loop          | Signal             | Where to Measure    | Frequency   | Level            |

|---------------|--------------------|---------------------|-------------|------------------|

| Reference Sum | HF Reference       | W38 (964) to A6A6J2 | Table 8-209 | -3 dBm           |

|               | 10/20 Reference    | W37 (973) to A6A5J1 | Table 8-209 | -4 dBm           |

| Output Sum    | FM Sum Loop Output | W28 (961) to A6A4J1 | 10-20 MHz   | -3 clBm          |

|               | RS Loop Output     | W43 (965) to A6A7J1 | Table 8-209 | +3 to<br>-13 dBm |

Table 8-206. HF Loops Input Signals

| Table 8-207 Out | tput Sum | Loop VCC | Pretuning | Check | (A8A1) |

|-----------------|----------|----------|-----------|-------|--------|

|-----------------|----------|----------|-----------|-------|--------|

| Front Panel<br>Frequency<br>Setting (MHz) | VCO Frequency *<br>( <u>+</u> 3 MHz) | Bit On | Tuning Voltage<br>( <u>+</u> 1.0 Vdc)<br>A6A4J2 | Inductor On |

|-------------------------------------------|--------------------------------------|--------|-------------------------------------------------|-------------|

| 524.0                                     | 527.5                                | None   | -36.10                                          | Е           |

| 523.0                                     | 526.0                                | Pl     | -33.40                                          | E           |

| 521.0                                     | 524.5                                | P2     | -30.70                                          | E           |

| 517.0                                     | 520.5                                | P4     | -26.20                                          | Е           |

| 511.0                                     | 514.5                                | P8     | -19.70                                          | E           |

| 452.0                                     | 456.0                                | All    | -13.00                                          | D&C         |

| 330.0                                     | 334.0                                | None   | -36.10                                          | A           |

| 344.0                                     | 347.0                                | None   | -36.10                                          | В           |

| 370.0                                     | 375.0                                | None   | -36.10                                          | l c         |

| 421.0                                     | 426.0                                | None   | -36.10                                          | D           |

| 524.0                                     | 527.5                                | None   | -36.10                                          | Ċ           |

| Table 8-208. Reference | e Sum | Loop | VCO | Pretuning | Check | (A8A2) |  |

|------------------------|-------|------|-----|-----------|-------|--------|--|

|------------------------|-------|------|-----|-----------|-------|--------|--|

| Front Panel<br>Frequency<br>Setting (MHz) | VCO Frequency*<br>( <u>+</u> 3 MHz) | Bit On | Tuning Voltage<br>( <u>+</u> 1.0 Vdc)<br>A6A4J2 | Inductor On |

|-------------------------------------------|-------------------------------------|--------|-------------------------------------------------|-------------|

| 340.0                                     | 336.5                               | None   | -36.10                                          | A           |

| 350.0                                     | 346.5                               | P4     | -26.60                                          | В           |

| 380.0                                     | 376.0                               | None   | -36.10                                          | С           |

| 430.0                                     | 425.5                               | Pl     | -33.40                                          | Ď           |

| 520.0                                     | 516.0                               | P8     | -19.70                                          | Е           |

| 530.0                                     | 525.5                               | P2     | -30.70                                          | E           |

8-219

| Front Panel<br>Frequency<br>Setting (MHz) | Reference Sum Loop<br>Output (MHz)<br>W43 (965) to A6A7Jl | 10/20 MHz Reference<br>W37 (973) to A6A5J1 | HF Reference (MHz)<br>W38 (964) to A6A6J2 |

|-------------------------------------------|-----------------------------------------------------------|--------------------------------------------|-------------------------------------------|

| 32X.X                                     | 310.0                                                     | 10.0                                       | 320.0                                     |

| 33X.X                                     | 320.0                                                     | 20.0                                       | 340.0                                     |

| 34X.X                                     | 330.0                                                     | 10.0                                       |                                           |

| 35X.X                                     | 340.0                                                     | 20.0                                       | 360.0                                     |

| 36X.X                                     | 350.0                                                     | 10.0                                       |                                           |

| 37X.X                                     | 360.0                                                     | 20.0                                       | 380.0                                     |

| 38X.X                                     | 370.0                                                     | 10.0                                       |                                           |

| 39X.X                                     | 380.0                                                     | 20.0                                       | 400.0                                     |

| 40X.X                                     | 390.0                                                     | 10.0                                       |                                           |

| 41X.X                                     | 400.0                                                     | 20.0                                       | 420.0                                     |

| 42X.X                                     | 410.0                                                     | 10.0                                       |                                           |

| 43X.X                                     | 420.0                                                     | 20.0                                       | 440.0                                     |

| 44X.X                                     | 430.0                                                     | 10.0                                       |                                           |

| 45X.X                                     | 440.0                                                     | 20.0                                       | 460.0                                     |

| 46X.X                                     | 450.0                                                     | 10.0                                       |                                           |

| 47X.X                                     | 460.0                                                     | 20.0                                       | 480.0                                     |

| 48X.X                                     | 470.0                                                     | 10.0                                       |                                           |

| 49X.X                                     | 480.0                                                     | 20.0                                       | 500.0                                     |

| 50X.X                                     | 490.0                                                     | 10.0                                       |                                           |

| 51X.X                                     | 500.0                                                     | 20.0                                       | 520.0                                     |

| 52X.X                                     | 510.0                                                     | 10.0                                       |                                           |

| 53X.X                                     | 520.0                                                     | 20.0                                       | 540.0                                     |

| 54X.X                                     | 530.0                                                     | 10.0                                       |                                           |

| 55X.X                                     | 540.0                                                     | 20.0                                       | 560.0                                     |

| 56X.X                                     | 550.0                                                     | 10.0                                       |                                           |

| 57X.X                                     | 560.0                                                     | 20.0                                       | 580.0                                     |

| 58X.X                                     | 570.0                                                     | 10.0                                       |                                           |

| 59X.X                                     | 580.0                                                     | 20.0                                       | 600.0                                     |

| 60X.X                                     | 590.0                                                     | 10.0                                       |                                           |

| 61X.X                                     | 600.0                                                     | 20.0                                       | 620.0                                     |

| 62X.X                                     | 610.0                                                     | 10.0                                       |                                           |

| 63X.X                                     | 620.0                                                     | 20.0                                       | 640.0                                     |

Table 8-209. Reference Sum Loop Variable Frequency Signals

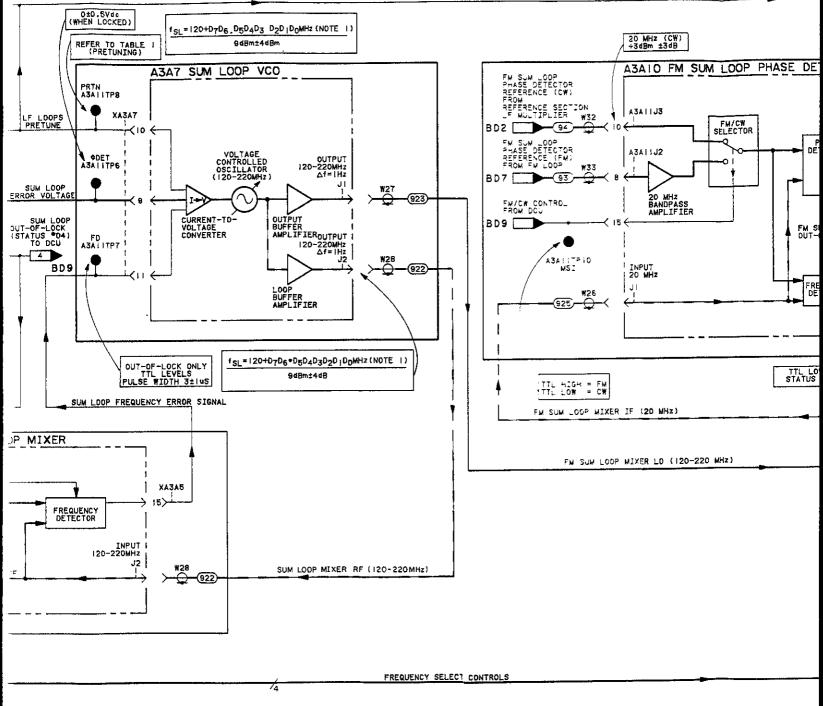

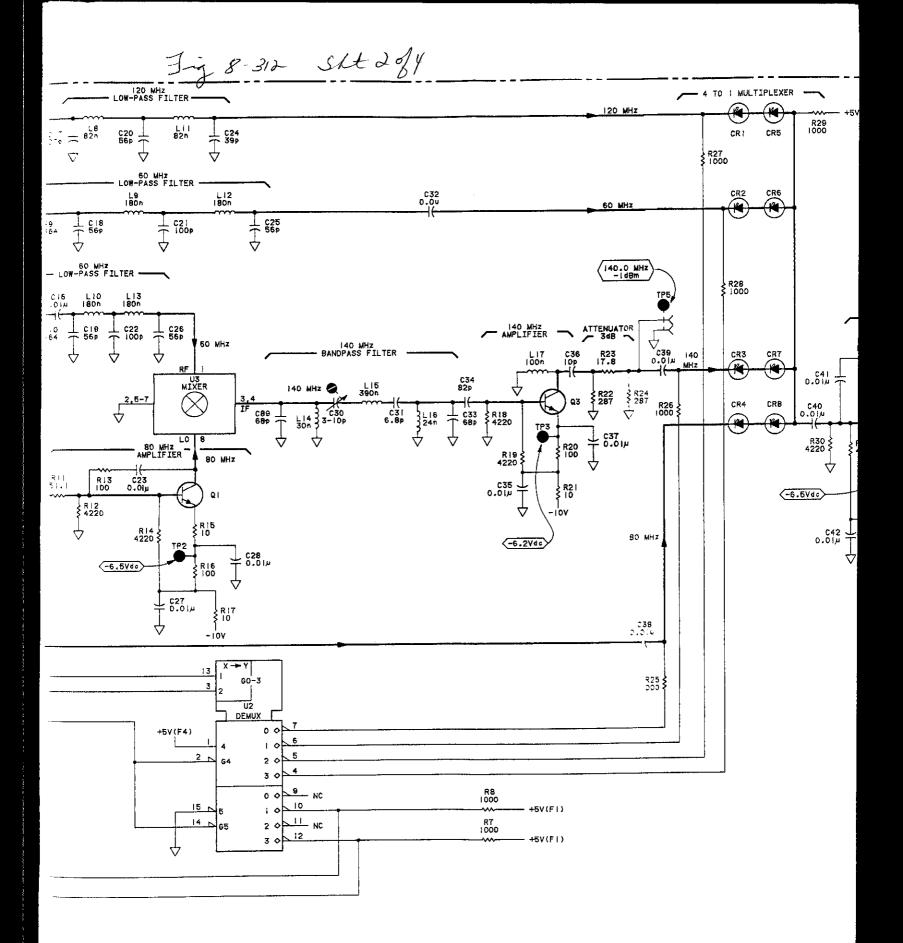

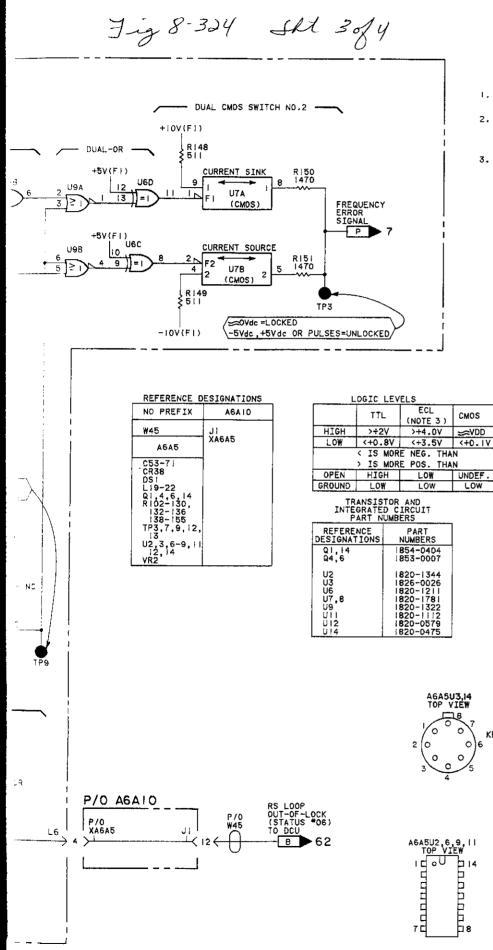

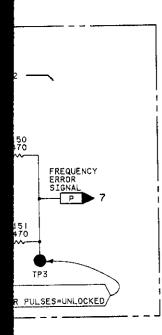

Jig 8-204 Sht 294

7-ig 8-204 Sht 3 of 4

7,8

.

Model 8663A

SERVICE SHEET BD4 FRACTIONAL-N LOOP BLOCK DIAGRAM

REFERENCE BD1

Simplified Operation (Section III) Operator's Checks (Section III) Table 4-1. Recommended Performance Tests After Adjustments or Repairs. Table 5-2. Post-Repair Adjustment Procedures.

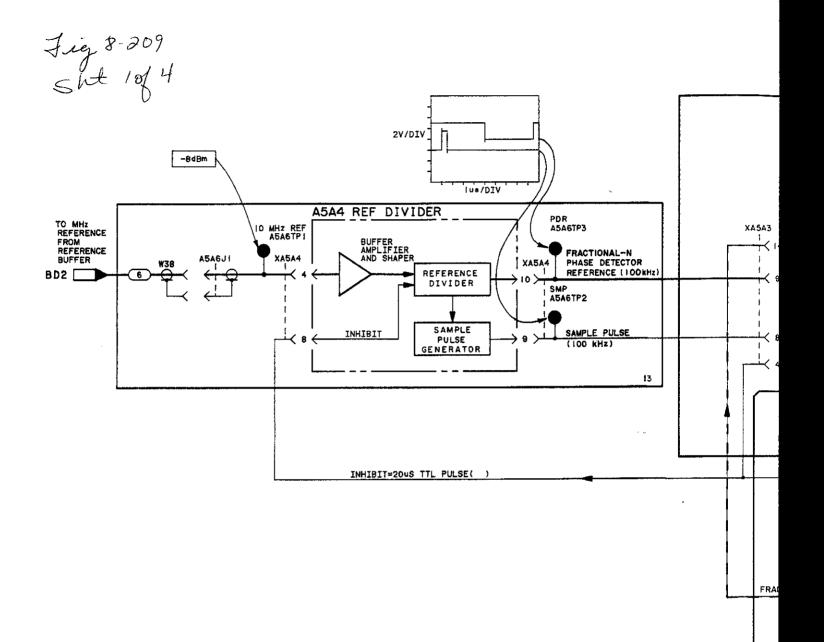

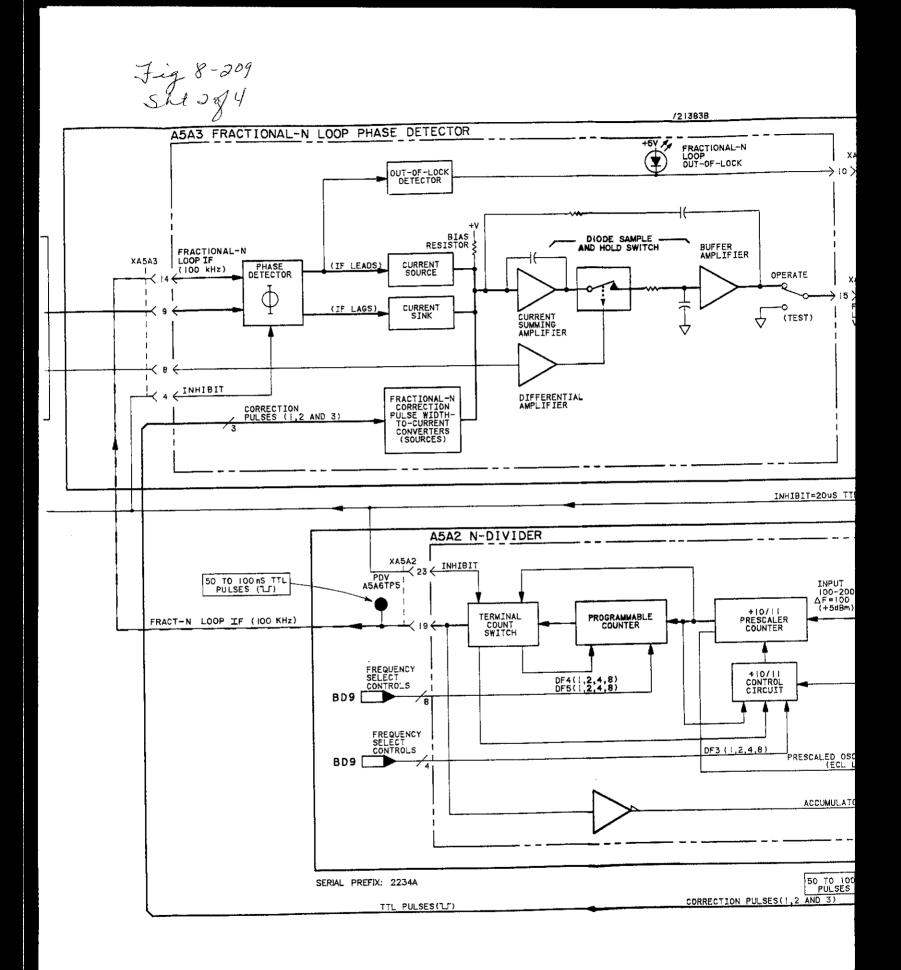

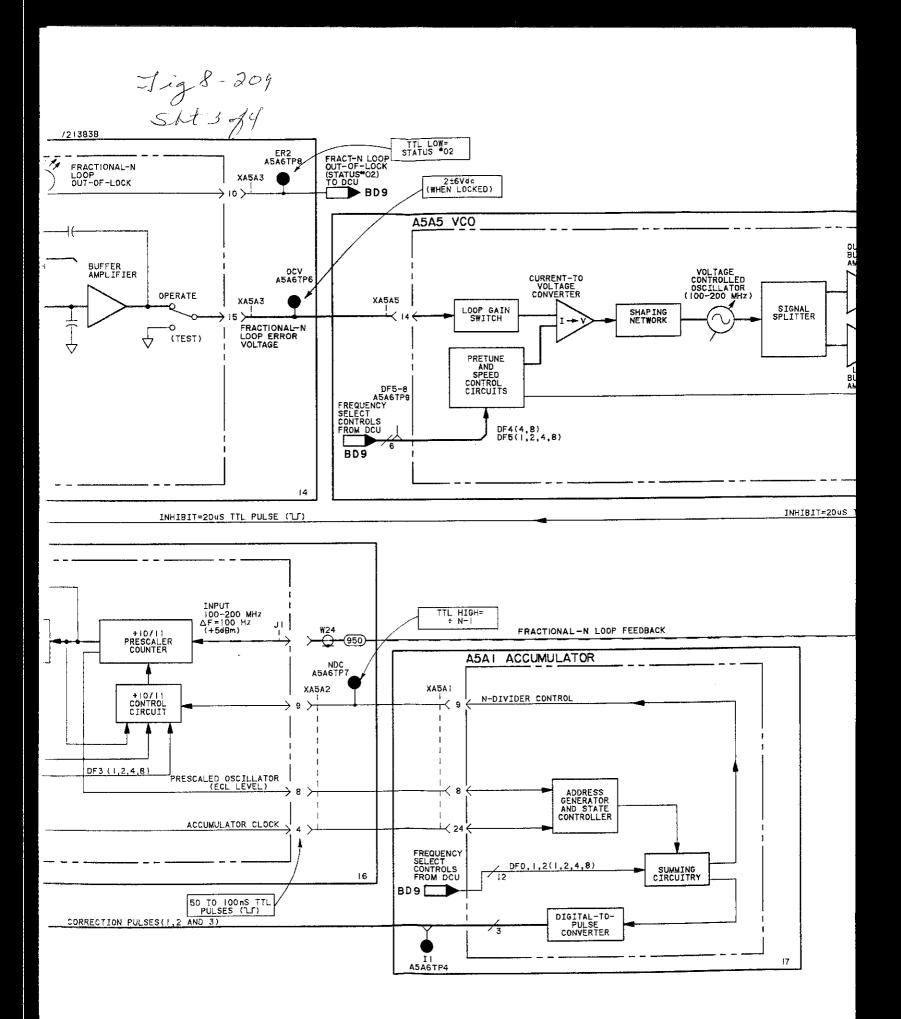

#### PRINCIPLES OF OPERATION

The Fractional-N Loop (FN Loop) generates frequencies from 100 to 200 MHz in 100 Hz steps using a 100 kHz reference. The 100 kHz reference is derived by dividing the 10 MHz output signal from the Reference Section. The output frequency from this section is a function of front panel frequency digits  $D_5$ ,  $D_4$ ,  $D_3$ ,  $D_2$ ,  $D_1$ , and  $D_0$  (that is, the six least significant digits) in the Generator's basic frequency band (that is, 320-640 MHz). The three least significant digits,  $D_2 - D_0$ , represent the fractional portion of the frequency while the next three digits ( $D_5 - D_3$ ) contain the integer portion of the frequency. To determine the FN Loop VCO frequency from the front panel frequency display (RF OUTPUT frequency) use the following formula:

The Fractional-N Loop uses a frequency synthesis technique known as Fractional N. With only one phase lock loop the FN Loop can produce signals with far greater frequency resolution than the traditional N Loop. In an N Loop, the VCO is restricted to only work at frequencies N times the reference frequency. Therefore, it can only generate signals that are integer multiples of the reference frequency (VCO Freq. = N x Ref Freq.).

The FN Loop is very similar to the N Loop. It contains all the basic elements of the N Loop with the addition of several new elements. In fact, if the selected frequency does not have a fractional part (that is, when  $D_2 - D_0$  are zeros), the FN Loop works like the N Loop.

Figure 8-205 is a simplified block diagram of a Fractional-N phase lock loop with the shaded area containing the Fractional-N elements.

The major difference between the FN Loop and the N Loop is that the FN Loop VCO is not restricted to operating at only N times the reference frequency, but can also operate at frequencies that are fractional multiples of the reference frequency. The frequency resolution of the FN Loop is 100 Hz which means the FN VCO is capable of operating at a fractional multiple of 0.001 of the reference signal (0.001 of 100 kHz = 100 Hz).

Figure 8-205. Simplified Block Diagram of Fractional–N Loop

Assume that the VCO frequency desired is 199.9900 MHz. In a traditional N Loop it would be impossible to phase lock the loop, since the desired VCO frequency, 199.9900 MHz, is a fractional multiple (1999.9) of the reference frequency. In order to phase lock the loop, the VCO frequency divided by N (VCO/N) must equal the 100 kHz reference signal. This would require an N that had a fractional component (N = 1999.9).

In the FN Loop, division by a fractional component is possible. The N Divider (A5A2) cannot divide by a fractional component directly but it is capable of changing from an N to an N-1 divider. Fractional division is accomplished by dividing by an integer (N) for the number of times and one less than the integer (N-1) for a number of times. The fractional N is then the average of N and N-1. For example, if an N of 1999.9 is required, the N Divider divides by 2000 (N) nine times and by 1999 (N-1) one time. This dividing between N and N-1 results in an average N of 1999.9.

A method of determining when to divide by N or N-1 is required. This is the purpose of the Accumulator (A5A1). When the FN Loop is operating with a fractional part, the VCO/N signal no longer equals the reference frequency, hence the phase difference between the two signals starts to increase. When analyzing the phase relationship between the reference and VCO/N signals, it is better to view it in terms of reference periods. A reference period is defined as the time required for the reference signal to complete one cycle (10 us). The Accumulator does not actually measure the phase difference but it computes what the phase difference should be after each reference period.

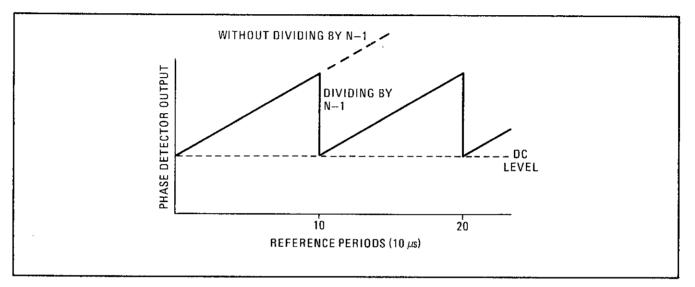

Since the phase difference is continuously increasing each reference period, the output from the phase detector is continuously increasing. In an N Loop the error voltage from the phase detector is used to tune the VCO frequency in a direction to reduce the phase difference or error. However, in the FN Loop, the phase difference is allowed to increase until the total or accumulated phase difference reaches or exceeds one full VCO cycle (360 degrees) of phase. Prior to the reference period that the phase difference reaches or exceeds one full cycle, the Accumulator generates an N Divider Control (NDC) signal causing the N Divider to divide by one less than the previous N.

Dividing the FN VCO frequency by N-1 instead of N causes the N Divider to reach its terminal count one VCO period sooner. This effectively advances the VCO/N signal one VCO period which counteracts or cancels the previous phase advancement.

When the N Divider divides by a number N, the VCO/N signal starts to lag the reference signal. When the phase difference between the reference signal and the VCO/N signal reaches or exceeds one cycle of phase, the N Divider is programmed to divide by N-1 which now causes the VCO/N signal to lead the reference signal. The resulting averaged VCO/N signal equals the reference frequency and the loop can be phase-locked even though the instantaneous VCO frequency is not an integer-multiple of the reference.

In the example in Figure 8-206, the FN VCO is operating at 199.9900 MHz. That would require that the N Divider divide by an N equal to 1999.900. The N Divider is not capable of dividing by 1999.900 but it can divide by 2000 or 1999. The N Divider starts out dividing by 2000. Since the VCO operates at 199.9900 MHz and N = 2000, the VCO/N signal to the phase detector would be 99.9950 kHz. Note, the phase of the VCO/N signal starts to lag the 100 kHz reference frequency which causes the phase detector to output an ever increasing dc level.

As the reference signal goes through one cycle, the VCO (operating 1999.9 times faster) goes through 1999.9 cycles. For comparison, an N Loop circuit is also examined.

In an N Loop, if N = 2000 and reference = 100 kHz, the VCO frequency must equal 200.0 MHz to maintain phase lock. This means the N Loop goes through 2000.0 cycles for each reference period. Note the phase difference between the FN and N Loop VCO's after one reference period. The FN Loop lags the N Loop by 0.1 cycle which represents the fractional part of the frequency. To put it another way, the FN Loop VCO decreases by one tenth of a cycle relative to its integer part (N Loop) for every reference period. After the passage of two reference periods the FN VCO will have gone through 3999.8 cycles and the phase difference will have increased to 0.2 cycles. After each reference period the phase difference will increase by another 0.1 cycle. Table 8-210 illustrates this point.

After ten reference periods, the phase difference between the VCO/N and reference signals will have increased exactly one VCO cycle. Prior to the reference period that the phase difference reaches one VCO cycle, the N Divider receives an NDC command from the Accumulator. This causes the N Divider to divide by 1999 (one integer less than 2000). This has the effect of cancelling the previous phase difference, hence the VCO/N frequency averaged over ten reference periods now equals the 100 kHz reference and therfore the loop can be phase locked.

| Number of<br>Reference<br>Periods | Cycles Per       | Phase Difference                             |                   |  |

|-----------------------------------|------------------|----------------------------------------------|-------------------|--|

|                                   | N-Loop = 200 MHz | FN Loop = $199.99$ MHz<br>(Fraction N = 0.1) | (Cycles of Phase) |  |

| 1                                 | 2000             | 1999.9                                       | 0.1               |  |

| 2                                 | 4000             | 3999.8                                       | 0.2               |  |

| 3                                 | 6000             | 5999.7                                       | 0.3               |  |

| 4                                 | 8000             | 7999.6                                       | 0.4               |  |

| 5                                 | 10000            | 9999.5                                       | 0.5               |  |

| 6                                 | 12000            | 11999.4                                      | 0.6               |  |

| 7                                 | 14000            | 13999.3                                      | 0.7               |  |

| 8                                 | 16000            | 15999.2                                      | 0.8               |  |

| 9                                 | 18000            | 17999.1                                      | 0.9               |  |

| 10                                | 20000            | 19999.0                                      | 1.0               |  |

| Table 8-210. | Phase | Difference | Versus | Reference | Periods |

|--------------|-------|------------|--------|-----------|---------|

|--------------|-------|------------|--------|-----------|---------|

This example uses a fractional N of 0.1. As another example, suppose the FN Loop VCO frequency was equal to 150.0050 MHz. This represents a fractional N of 0.95. For this example, the N Divider divides by N-1 (1500) nineteen out of twenty reference periods.

Continuously dividing by N and N-1 causes the phase detector to output a sawtooth waveform riding on a dc level. As shown in Figure 8-206, the output from the phase detector increases linearly (ramps) as the phase difference increases. The output continues to increase until the N Divider divides by N-1 which cancels the previous phase difference. This causes the output of the phase detector to return to its initial level.

The dc voltage level on which the sawtooth waveform is riding represents the proper tune voltage to phase-lock the VCO to the reference. Any ac components (sawtooth) on the dc tune voltage would prevent phase-lock and cause frequency modulation. To counteract this sawtooth waveform, an equal but opposite ac signal is generated by the Fractional-N Correction Pulse Width-to-Current Converters. This signal is then summed with the phase detector output to cancel the sawtooth components, leaving only the desired dc tuning voltage.

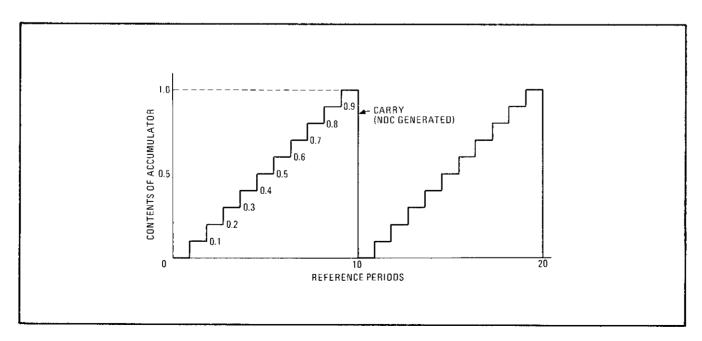

The fractional portion of the VCO frequency contains the information needed to develop the signal that counteracts the changing phase detector output. The fractional part of the frequency is presented to the Accumulator in BCD form. Once during each reference period the contents of the Accumulator are incremented by the fractional part. The number stored in the Accumulator corresponds to the difference in phase between the VCO/N and the reference signal. 8-226

Since the Accumulator is incremented each reference period, its contents represent an instantaneous fractional sum which grows until one VCO cycle of phase difference has occurred. The contents of the Accumulator as viewed with respect to time is shown in Figure 8-207. The contents of the Accumulator can be represented by a staircase ramp resetting each reference period when the N Divider divides by N-1. Note that the contents of the Accumulator when viewed graphically have the same characteristics as the sawtooth output from the phase detector.

Figure 8-206. Phase Detector Output

Figure 8-207. A Pictorial View of the Contents of the Accumulator

The numbers stored in the Accumulator are in BCD form. First the BCD information is inverted and then converted into signals with varying pulse widths. These signal lines are labeled Correction Pulse 1, 2, and 3. The Correction Pulses are then fed into the Pulse Width-to-Current Converter circuit which is located on the Fractional-N Loop Phase Detector Assembly (A5A3). The outputs from the Pulse Width-to-Current Converter circuit is then summed with the output from the phase detector. This cancels the sawtooth portion of the output from the phase detector leaving only a clean dc tuning voltage for the VCO.

#### TROUBLESHOOTING

When a problem has been traced to the Fractional-N Loop or the instrument status code gives error 02, use the following procedure to isolate the problem to an assembly.

- 1. Check the 10 MHz reference signal at motherboard test point TP1. This signal should be the level shown on the block diagram.

- 2. Pull out the A5A1 Accumulator assembly. This removes the fractional part of the loop. Set the front panel frequency to 320.050 050 0 MHz. The loop should lock at a frequency of 149.0 MHz. Measure this frequency with a counter at A5A5J2. If the loop does lock, the Accumulator assembly is defective. If the loop doesn't lock, leave the Accumulator assembly out and continue with the next step.

- 3. Move the switch on the A5A3 Phase Detector Assembly to the TEST position. This opens the loop so that only the pretuning circuitry is driving the VCO. Set the Front panel frequency to the values in Table 8-211 and measure the VCO frequency at A5A5J2. This tests all the bits in the pretuning by turning on but one at a time.

| Front Panel<br>Frequency Setting<br>(MHz) | Pretuning Bit On | A5A5 VCO Frequency<br>Measured at A5A5J2<br>(MHz <u>+</u> 3 MHz) |  |

|-------------------------------------------|------------------|------------------------------------------------------------------|--|

| 320.011                                   | All              | 102                                                              |  |

| 320.080                                   | D5-8             | 122                                                              |  |

| 320.040                                   | D5-4             | 162                                                              |  |

| 320.020                                   | D5-2             | 182                                                              |  |

| 320.010                                   | D5-1             | 192                                                              |  |

| 320.008                                   | D4-8             | 194                                                              |  |

| 320.004                                   | D4-4             | 198                                                              |  |

| 320.0                                     | None             | 202                                                              |  |

| Table | 8-211. | Fractional-N | Loop | Troubleshooting |

|-------|--------|--------------|------|-----------------|

|-------|--------|--------------|------|-----------------|

If all these frequencies are within limits, the VCO and pretuning are good. This is most of the A5A5 assembly so proceed to the next step. If one or more frequencies are bad, the problem is on the A5A5 assembly.

- 4. Measure the PDV signal from the A5A2 N Divider Assembly at TP5 on the motherboard. The frequency of this signal should be 100 kHz <u>+</u> 5 kHz. Use an oscilloscope to check that levels of this signal are valid TTL levels (high is greater than 2.4 Vdc and low is less than 0.8 Vdc). If this signal is correct, the A5A2 assembly is operating properly, otherwise, there is a problem on the A5A2.

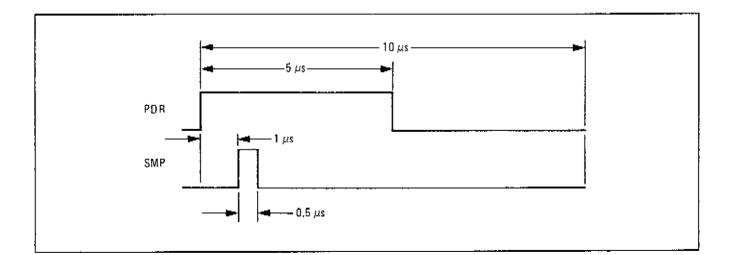

- 5. Measure the PDR and SMP signals from the A5A4 Reference Divider Assembly on the motherboard at TP3 (PDR) and TP2 (SMP). The frequency of both these signals should be 100.0 kHz. Look at the waveforms on an oscilloscope to check for valid TTL levels and the timing relationship between the waveforms as shown in Figure 8-208.

If these signals are correct, the A5A4 is operating properly, otherwise, there is a problem on A5A4.

6. If all the previous checks do not show any problems, the A5A3 Phase Detector is the most likely cause of the problem.

Figure 8-208. Timing Diagram for 100.0 kHz PDR and SMP Signals

02

8-231/232

Model 8663A

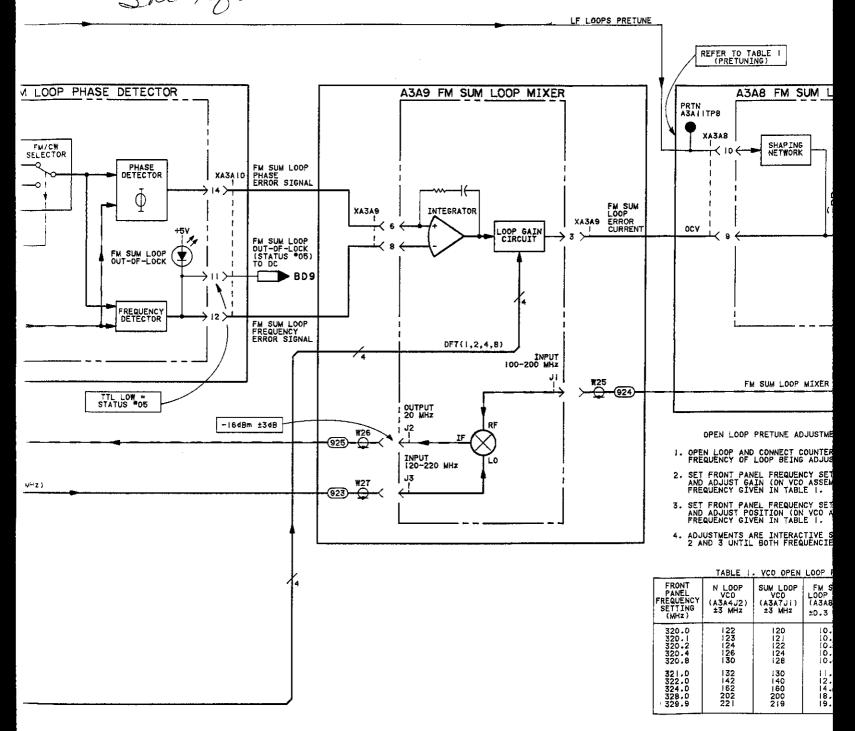

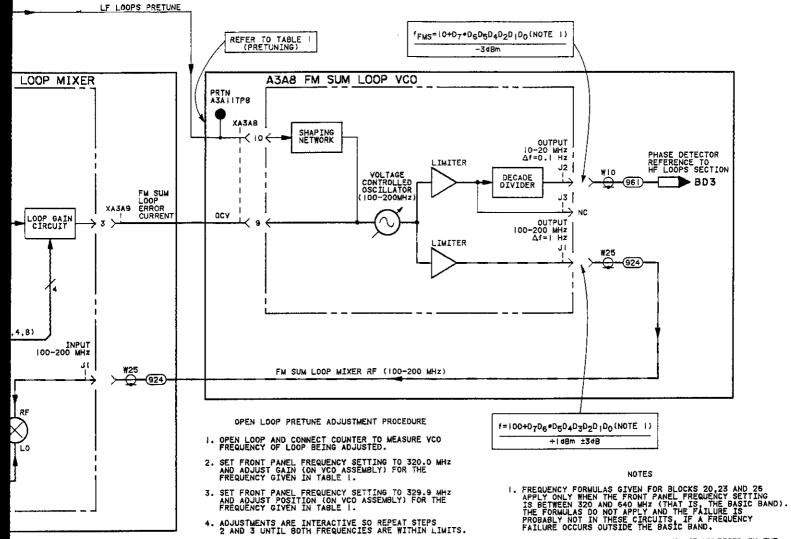

SERVICE SHEET BD5 LOW FREQUENCY LOOPS BLOCK DIAGRAM

REFERENCE BD1

Simplified Operation (Section III) Operator's Checks (Section III) Table 4-1. Recommended Performance Tests After Adjustments or Repairs. Table 5-2. Post-Repair Adjustment Procedures.

# PRINCIPLES OF OPERATION

The Low Frequency Loops Section serves two functions. First, it produces the 10 MHz to 20 MHz reference signal which is sent to the input of the phase detector (in the Output Sum Loop of the High Frequency Loops Section) so that the 320 MHz to 640 MHz, 0.1 Hz step resolution, fundamental frequency band can be generated. Secondly, if FM is desired at the output, it is summed in at this point.

The Low Frequency Loops are composed of three principal sections: the N Loop, the Low Frequency Sum Loop, and the FM Sum Loop. Each is a discrete phase lock loop. The N Loop takes the 10 MHz reference signal (which must be greater than +7 dBm) and multiplies it, using fractional-N synthesis, to a frequency band of 122 MHz to 221 MHz (1 MHz step resolution). This frequency is related to the 1 MHz and 0.1 MHz digits of the front panel frequency display (D7 and D6 in the basic frequency band).

The signal from the N Loop is sent to the Low Frequency Sum Loop where it is locked to the signal from the Fractional-N Loop (Service Sheet BD4). This signal varies between 100 MHz and 200 MHz (100 Hz step resolution), but is divided by two decade counters (divide by 100) in the Low Frequency Sum Loop so that it varies between 1 MHz and 2 MHz (with 1 Hz resolution) at the input ot the phase detector. The output of the Low Frequency Sum Loop (120 MHz to 220 MHz, 1 Hz step resolution) is sent to the FM Sum Loop.

In the FM Sum Loop, the signal is summed with either a 20 MHz continuous wave (CW) signal from the Reference Section or a 20 MHz frequency modulated signal from the Modulation Section (Service Sheet BD7). The output of this loop is a 100 MHz to 200 MHz (1 Hz step resolution) signal which is passed through a decade divider before leaving the board. The output of the decade divider is a frequency band which extends from 10 MHz to 20 MHz in 0.1 Hz steps. This signal is sent to the phase detector in the Output Sum Loop of the High Frequency Loops Section at 0 dBm to +16 dBm.

Model 8663A

### TROUBLESHOOTING

## General

There are three phase lock loops in this section. The hierarchy is:

- N Loop (Error code 03)

- Sum Loop (Error code 04)

- FM Sum Loop (Error code 05)

There is a separate troubleshooting procedure for each loop. If more than one of the loops is unlocked, always start with the highest order unlocked loop because it will cause the lower order loops to be unlocked. If the front panel status display gives a hardware malfunction code of 03, 04, or 05, then this code indicates at which loop to start troubleshooting.

#### N-Loop Troubleshooting

When it has been determined that there is a problem in the Low Frequency N Loop by troubleshooting on the Overall Block Diagram (Service Sheet BD1) or the out-of-lock indicator being lit, perform the following sequence to isolate the defective assembly:

- 1. Unplug the A3A3 assembly and remove it from the instrument. This opens the loop and leaves the A3A4 assembly being driven by only the pretune voltage from A3A6. Set the front panel frequency to the values in the first column of the table on the block diagram. Measure the VCO frequency at A3A4J2 and compare it to the normal values given in the table. Each frequency setting turns on one bit of the eight which drive the pretune circuitry. If the VCO frequencies are correct, the A3A4 VCO assembly is operating properly and the A3A3 divider/phase detector assembly is the likely cause of the problem. In this case, proceed to Service sheet 18 and troubleshoot the A3A3 assembly.

- 2. When the VCO frequencies are not correct, proceed with the Sum Loop troubleshooting.

### Sum Loop Troubleshooting

When it has been determined that there is a problem in the Low Frequency Sum Loop by troubleshooting on the overall block diagram (Service Sheet BD1) or the out-of-lock indicator being lit, perform the following sequence to isolate the defective assembly:

1. Remove the two jumpers on the A3A7 VCO Assembly and plug the board back into its socket. Removing these jumpers opens the loop and the VCO is driven only by the pretuning voltage from the A3A6 assembly.

- 2. Set the front panel frequency to the values in the first column of the table on the block diagram. Measure the VCO frequency at A3A7J1 and compare to the normal values given in the table. Each frequency setting turns on one bit of the eight which drive the pretune circuitry. If the VCO frequencies are correct, the A3A7 VCO is operating properly so proceed to step 4 to continue troubleshooting.

- 3. When the VCO frequencies are not correct, try the following:

- a) Perform the open-loop pretune adjustment procedure on the block diagram. If these adjustments can be made, repeat step 2. Otherwise, continue below.

- b) Measure the pretune voltage (TP8 on the motherboard) for the front panel frequency settings given in the table on the block diagram. If these voltages are not normal, trace the problem starting with the pretune circuitry on A3A6.

If the open-loop pretune adjustments cannot be made but the pretune voltages (TP8) are normal, the A3A7 VCO is faulty.

4. Set the front panel frequency to 320.0 MHz. Adjust the GAIN control on A3A7 to set the VCO output frequency at A3A7J2 to 120.0 <u>+0.5 MHz</u>. The W23 cable must be in place on A3A7J2.

Check the following:

- a) a 2.0  $\pm$ 0.5 MHz signal at TP5 on the motherboard. Amplitude >3 Vp-p.

- b) A steady TTL low signal at TP7 on the motherboard. This is the frequency detector output.

- c) A steady TTL low signal at pin 11 of A3A5. This is the out-of-lock signal from A3A6 which should be active (low) when the loop is open.

- 5. Turn the A3A7 GAIN adjustment counter-clockwise (CCW) while monitoring the frequency of the mixer output at TP5 on the motherboard. Turning the GAIN adjustment CCW increases the VCO frequency. The N Loop output is at 122 MHz so the mixer output (TP5) should decrease in frequency, reach zero and begin increasing. When the frequency reaches zero and begins to increase, check TP7 on the motherboard for positive going TTL pulses. This is the output of the frequency detector and pulses indicate that the VCO is higher than the N Loop output.

If any of these checks gives abnormal results, the problem is likely on the A3A5 assembly, otherwise, the A3A6 Phase Detector assembly is the likely cause of the problem. Service

# FM Sum Loop Troubleshooting

When it has been determined that there is a problem in the FM Sum Loop by troubleshooting on the overall block diagram (Service Sheet BD1) or the out-of-lock indicator being lit, perform the following sequence to isolate the defective assembly:

- 1. Pull the A3A9 Mixer assembly up far enough so that the bottom edge connector is completely out of the motherboard connector, but leave all the RF cables connected to the top of the assembly. This opens the loop by disconnecting the phase detector drive circuitry but leaves the mixer connected. In this condition, the VCO is only driven by the pretune voltage from A3A6. Set the front panel frequency to the values in the first column of the table in the block diagram. measure the A3A8 VCO frequency at A3A8J3 and compare it to the normal values given in the table. Each frequency setting turns on one bit of the eight which drive the pretune circuitry.

- 2. If the VCO frequencies are correct, the A3A8 VCO is operating properly. Check that the outputs at A3A8J1 and A3A8J2 are the proper level as stated on the block diagram. Notice that the frequency at A3A8J2 is one-tenth that of the other outputs. Proceed to step 3 to continue troubleshooting. When the VCO frequencies are not correct, try the following:

- a) Perform the open-loop pretune adjustment procedure on the block diagram. If these adjusments can be made, repeat the VCO check. Otherwise, continue below.

- b) Measure the pretune voltage (TP8 on the motherboard) for the front panel frequency settings given in the table on the block diagram. If these voltages are not normal, trace the problem starting with the pretune circuitry on A3A6.

If the open-loop pretune adjustments cannot be made but the pretune voltages (TP8) are normal, the A3A8 VCO is faulty.

- 3. Measure the output of the mixer at A3A9J2. Set the front panel frequency to the values in the first column of the table on the block diagram. The loop should still be opened by having A3A9 out of the motherboard socket. The frequency output of the mixer should be 20 MHz <u>+</u> 4 MHz for all front panel frequency settings, and the level should be as stated on the block diagram. If correct, the mixer portion of A3A9 is good. Connect cable W27 to A3A9J2 but leave A3A9 out of the cottom connector.

- 4. The phase detector on A3A10 is a double balanced mixer so the frequency of the output will be the difference between a 20 MHz reference signal and the nominal 20 MHz IF signal from the mixer on A3A9. Using any front panel frequency setting, vary the GAIN adjustment on the top of A3A8 VCO assembly to vary the frequency of the IF signal. Turning the GAIN adjustment clockwise increases the frequency of the IF signal. The normal cable must be connected to A3A9J2 but the IF signal can be monitored there with the <u>high impedance</u> of a counter by using a T adaptor. Vary

the input IF frequency above and below 20 MHz and look for the difference signal at A3A10 pin 14.

5. Monitor the frequency detector output at A3A10 pin 12. Vary the IF signal frequency using the A3A8 GAIN adjustment and check the frequency detector output with the values shown in Table 8-212.

The GAIN adjustment is coarse so the IF signal frequency cannot be controlled precisely. The IF signal frequency limits in the table should be considered approximations. It is important to verify that three different output states of the frequency detector exist but not that they occur at precise values of IF frequency.